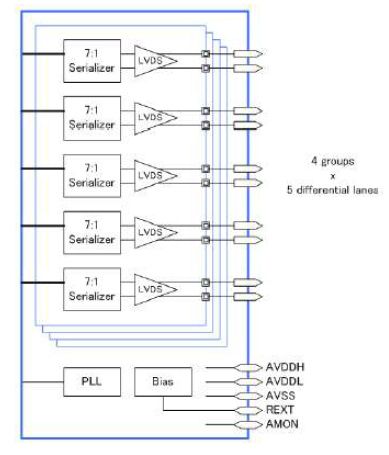

Based on internal equipment connections, the V-by-One® HS technology aims to transmit video signals at high data rates. The requirements to build a transmitter and receiver are laid out in the V-by-One®HS Standard. The available 8-lane and 16-lane PHYs for Tx and Rx support up to 4Gbps/lane. A transmitter for LVDS with a physical layer IP. Up to 1.5Gbps of data rate is supported by this IP, which comprises of 20-lane (4 x 4D1C) LVDS drivers.

LVDS compliant Tx

4 groups of 4-Data

1-Clock channels Each lane/group can be turned on/off individually Data/Clock can be assigned to any lane within the group

Differential polarity can be flip per lane

Supports from 168Mbps to 1.5Gbps data rate

Supports reduced swing mode

X7 Multiplier PLL for serial clock generation

Configurable analog characteristics

PLL loop filter

PLL VCO gain

Differential voltage Common-mode voltage

Pre-emphasis strength

Silicon Proven in GF 22nm FDX

Deliverables

Datasheet

Integration guideline

GDSII or Phantom

GDSII Layer map table

CDL netlist for LVS

LEF Verilog behavior model

Liberty timing model DRC/LVS/ERC results