Description

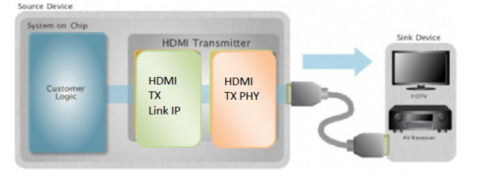

IP core for physical layer HDMI transmitters that fully complies with HDMI 1.4 specifications The HDMI transmitter PHY provides an easy-to-implement system LSI solution that supports pixel clocks between 25MHz and 250MHz for consumer devices like DVD player/recorders and camcorders. All of the Fab/Nodes listed below have undergone Silicon Proving: (TSMC, UMC, SMIC, GF, Samsung, ST). The HDMI Transmitter Link IP Core, which supports HDMI 1.4b and operates at 2.25 Gbps, 16-bit deep colour, and 3D compatibility, will be simple to incorporate into the SoC of consumer goods (HD-TV, AV receiver...etc.). The HDMI Rx IP's performance, functionality, and efficiency will be at their peak when connected to the HDMI Transmitter PHY IP. There are several HDMI Tx IP setups available.

Features

-

HDMI version 1.4 compliant transmitter

-

Supports DTV from 480i to 1080i/p HD resolution

-

Supports 24bit, 30bit and 36bit color depth per pixel

-

Integrated cable terminator

-

Adaptive equalizer for cable

-

Adjustable analog characteristics

-

PLL band width

-

VCO gain

-

BGR voltage

-

Cable terminator resistance value

-

DLL digital filter characteristics

-

Integrated Audio PLL

-

3.3V/2.5V/1.0V power supply

-

HDMI version 1.4a, HDCP revision 1.3 and DVI version 1.0 compliant receiver

-

Controller Supports DTV from 480i to 1080i/p HD resolution, and PC from VGA to UXGA

-

Supports 3D video format specified in HDMI 1.4a specification

-

Programmable 2-way color space converter

-

Compliant with EIA/CEA-861D

-

Deep color supported up to 16bit per pixel

-

xvYCC Enhanced Colorimetry

-

All packet reception including Gamut Metadata Packet

-

Supports RGB, YCbCr digital video output format including ITU.656

-

24/30/36/48bit RGB/YCbCr 4:4:4

-

16/20/24bit YCbCr 4:2:2

-

8/10/12bit YCbCr 4:2:2 (ITU.601 and 656)

-

48 bit mode is not supported in 1080p

-

Supports standard SPDIF output for stereo or compressed audio up to 192KHz

-

Support PCM, Dolby digital, DTS digital audio output through 4bits I2S up to 8 channel

-

IEC60958 or IEC61937 compatible

-

1bit audio format (Super Audio CD) output

-

High-bitrate compressed audio formats output

-

Slave I2C interface for DDC connection

-

Configuration registers programmable via synchronized parallel interface

-

Interface to external HDCP key storage

-

Silicon Proven in UMC 40SP.

Deliverables

-

GDS

-

Configurable RTL Code

-

HDL based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers and performance monitors

-

Configurable synthesis shell

-

Documentation

-

Design Guide

-

Verification Guide

-

Synthesis Guide

Benefits

-

Very Low power

-

Small Area, easy to integrate

-

Test chip and Test board available

Applications

-

Digital TV

-

Tablets

-

Mobile phones

-

Digital camera

-

Camcorders

-

Soundbars

-

Audio/Video Receivers

-

DVD players

-

Recorders

-

Streaming-media players

-

Set-top boxes

-

Home theater systems

-

Game consoles

![]()