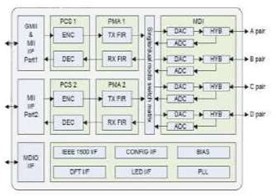

The GPHY is a fully integrated IP Core with low power consumption for Giga 10/100/1000 Ethernet applications. It can operate in 10BASE-T, 100BASE-TX, and 1000BASE-T protocols. By using GMII (Giga Media Independent Interface), this GPHY links to the Media Access Control Layer (MAC). By using RGMII or GMII (Giga Media Independent Interface), this GPHY interfaces to the Media Access Control Layer (MAC). It could support UTP5/UTP3 cable for 10BASE-Te Ethernet or Unshielded Twisted Pair Category 5 Cable (UTP5) for 100BASE-TX Fast Ethernet and 1000BASE-T Giga Ethernet. It includes the Physical Coding Sub-layer (PCS), Physical Medium Attachment Layer (PMA), and Twisted Pair Physical Medium Dependent Sub-layer (TP-PMD, 100BASE- TX only) as well as all of the physical layer functionality for 1000BASET as described by IEEE 802.3ab and 100BASE-TX, respectively.

IEEE 802.3-2008, IEEE 802.3az fully standards compliant

IEEE 1588-2008 support

BroadR-Reach™ support

Dual port MAC interface:

o GMII (10/100/1000BASE-T)

o MII (10/100BASE-T).

Auto-negotiation support

Automatic detection and correction of pair swaps (Auto-MDIX), pair skew and pair polarity

6 different operating modes:

1000BASE-T Full Duplex and Half Duplex

100BASE-TX Full Duplex and Half Duplex

10BASE-T Full Duplex and Half Duplex

Management interface

Baseline wander compensation

On-chip transmit wave-shaping

On-chip hybrid circuit

10KB jumbo frames

Internal, external and remote loop back

Hardware configuration for default operation

Power down mode, interrupt support

IEEE 1500 support for SoC testing integration.

LED indication: link mode, status, speed, activity, and collision Silicon Proven in SAM 14nm LPP

Deliverables

In-depth Product Datasheet

Verilog Behavioral Model (A) for Circuit Simulation

Liberty Format (db/.lib) for Synthesis, STA, and Equivalence Checks

CTL/CTLDB Integration for Design for Test (DFT)

SPF (STIL Procedure File) for ATPG Setup

LEF Files for Automated Place and Route (APR)

CDL Configuration for Layout Versus Schematic (LVS) Alignment