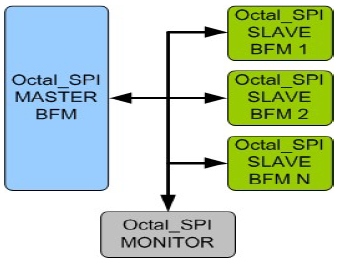

Description

The serial synchronous communication protocol is called octal SPI. It comes with a comprehensive test suite that covers the majority of potential scenarios. It executes all conceivable protocol tests in a guided or highly randomized manner, adding the opportunity to generate the greatest number of situations to successfully check the DUT. It is compatible with all Verilog simulators that support SystemVerilog and the Verilog HDL environment. Verilog, SystemVerilog, SystemC, VERA, Specman E, and non-standard verification environments all natively enable Octal SPI (Serial Peripheral Interface) Verification IP. An optional Smart Visual Protocol Debugger, a GUI-based debugger to speed up debugging, is included with Octal SPI (Serial Peripheral Interface) Verification IP.

Features

-

Follows Octal SPI basic specification as defined in Flash memory.

-

Supports Master and Slave Mode.

-

Supports Serial Peripheral Interface -- Mode 0

-

Supports below Protocol modes • Single I/O and Octa I/O • Support DTR (Double Transfer Rate) Mode

-

Supports clock frequency up to • Single I/O mode: 133MHz • Octa I/O mode: 133MHz

-

Supports below Input Data Format • SPI: 1-byte command code • OPI: 2-byte command code

-

Supports below Advanced Security Features

-

Block lock protection

-

Advanced Sector Protection (Solid and Password Protect)

-

Supports below Additional 8K bit security OTP • Features unique identifier • Factory locked identifiable, and customer lockable

-

Supports Command Reset. • Supports Electronic Identification

-

JEDEC 1-byte manufacturer ID and 2-byte device ID.

-

Supports Serial Flash Discoverable Parameters (SFDP) mode.

-

Supports 11-wire Slave interface.

-

Supports data width upto 8 bits.

-

Supports baud rate selection.

-

Supports single and burst transfer mode.

-

Supports constraints Randomization.

-

Supports backdoor initialization of data.

-

Built in functional coverage analysis.

-

Status counters for various events on bus.

-

Supports single, dual, quad and Octal bus width operation.

-

Supports Callbacks in Master, Slave and Monitor for various events.

-

Octal SPI Slave can be configured as standard device or can use FIFO for data passing.

-

Master contains rich set of commands for both standard device and FIFO model mode.

Deliverables

-

Complete regression suite containing all the Octal SPI testcases.

-

Examples showing how to connect various components and usage of Master, Slave and Monitor.

-

Detailed documentation of all classes, tasks and functions used in verification env.

-

Documentation contains User's Guide and Release notes.

![]()