Description

As Sensor data rate increases, there is a necessity to have control information flowing to and from sensors at an efficient data rate. Also, to bridge the gap of digital interface fragmentation of various interfaces like I2C/SPI/UART, MIPI has come up with a solution MIPI I3C interface. Also, the traditional interfaces like I2C/SPI/UART would require additional sideband signals like interrupts/chip select/enable/sleep signals. These additional signals increase the pin counts.MIPI I3C interface presents a fast, low cost, low power, two wire digital interfaces for sensors. Apart from increased data rate, I3C also has support for legacy devices operating in FM and FM+ modes. I2C-like communication with SCL clock speed up to 12.5 MHz MIPI-defined transmissions allowing the master to communicate with one or all slaves on the bus HDR mode using ternary number symbols to achieve two data transmissions per equivalent clock cycle. A subset of I2C communication to legacy I2C slaves, if present on the bus Slave initiated request to master, e.g. in-band interrupt, address request.

Features

-

Compliant with the MIPI Alliance Specification for I3C Version 1.0

-

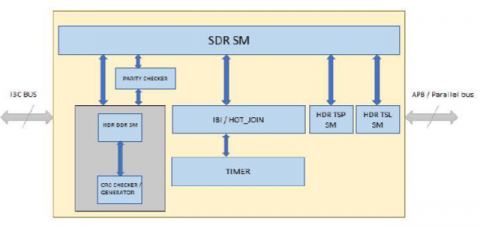

Supports modes of Master – SDR [12.5 MHz], HDR DDR and HDR- Ternary (TSP, TSL) Modes

-

Supports IBI, Hot Join

-

Dynamic Addressing assignment support

-

Supports asynchronous Mode 0, Mode 1

-

Compliant with AMBA 3 APB Protocol Specification v1.0 for register access

-

Easy integration and co-existence with I2C devices

-

Flexible protocol layer can be written on top of the core logic of I3C slave

-

Multiple I3C slave instances can be made

Deliverables

-

Configurable RTL Code

-

HDL-based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers, and performance monitors

-

Configurable synthesis shell

-

Documentation

-

Design guide

-

Verification guide

-

Synthesis guide

Benefits

-

I3C Master can be configured to work as the secondary master

-

I3C Slave configuration – HDR-DDR Slave, SDR-only Slave

-

System Access: APB or AXI

-

Configurable FIFOs

Applications

-

In Environmental sensing and other applications like NFC, etc.

-

Mechanical/Motion related application like to name a few: Compass/Magnetometer/Gyro/Accelerometer/Proximity/Touchscreen/ Grip/Time of Flight/Audi/ultrasonic, etc.

-

In biometrics/Health application like to name few: Fingerprint/glucometer/Heart-Rate, etc.

![]()