Description

I2C Verification IP provides a smart way to verify the I2C bi-directional two-wire bus. The I2C Verification IP is fully compliant with version 2.1, 3.0 and 6.0 of the Philip's I2C-Bus Specification and provides the following features. It is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env I2C Verification IP comes with optional Smart Visual Protocol Debugger which is GUI based debugger to speed up debugging.

Features

-

Supports 6.0 I2C specifications.

-

Full I2C Master and Slave functionality.

-

Start, repeat start and stop for all possible transfers.

-

Supports all I2C clocking speeds including HS mode, Fast mode, Fast mode plus and Ultra-fast mode.

-

7b/10b configurable Slave address.

-

Allows testing of various bus traffics for Read, Write, General Call and CBUS.

-

Supports complex sequence of 7/10 bit with repeated start command sequences.

-

Supports Bus-accurate timing.

-

Supports START byte generation and handling.

-

Supports Master/Slave arbitration and clock synchronization.

-

Supports Glitch insertion and detection.

-

Supports insertion of wait states by Slave and Master.

-

Supports AT24C1024 EEPROM memory model which supports 256 bytes Page Write Mode.

-

Supports Random and Sequential Read Modes.

-

Supports insertion of errors • Master aborting in middle of transaction. • Master doing ACK on last read access. • Master continues on NACK after write NACK from Slave. • Random and Periodic clock period stretching by Slave. • Random Write NACK insertion by Slave.

-

Glitch insertion on clock and data at various windows.

-

Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

-

Callbacks in Master and Slave for various events.

-

Status counters for various events in bus.

-

Functional coverage for complete I2C specifications.

-

I2C Verification IP comes with complete testsuite to test every feature of I2C specification.

Deliverables

-

Complete regression suite containing all the I2C testcases to certify I2C Master/Slave device.

-

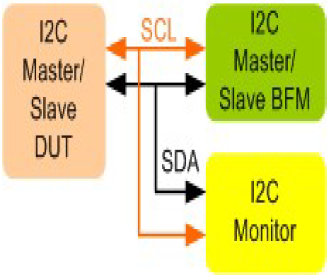

Examples showing how to connect various components, and usage of Master, Slave and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()