Description

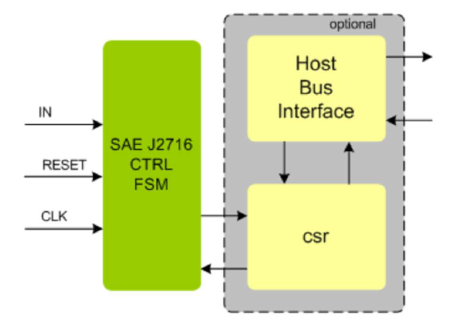

SAE J2716 Controller interface provides full support for the SENT SAE J2716 synchronous serial interface, compatible with SENT specification SAE J2716 APR2016. Through its SAE J2716 compatibility, it provides a simple interface to a wide range of lowcost devices. SAE J2716 Controller IP is proven in FPGA environment. The host interface of the SAE J2716 can be simple interface or can be AMBA APB, AMBA AHB, AMBA AHB-Lite, AMBA AXI, AMBA AXILite, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol. SAE J2716 Controller IP is supported natively in Verilog and VHDL

Features

-

Supports SENT specification SAE J2716 APRIL2016

-

Supports all types of frame reception • Short Serial Message Format • Enhanced Serial Message Format

-

Enhanced Serial Message Format supports two different configurations • 12-bit data and 8-bit message ID • 16-bit data and 4-bit message ID

-

Supports programmable clock frequency of operation

-

Supports programmable length for minimum nibble pulse period • Minimum nibble pulse period - 12 clock ticks • Maximum nibble pulse period - 27 clock ticks

-

Supports pause pulse properties • Minimum length - 12 clock ticks • Maximum length - 768 clock ticks

-

Supports both 4-bit CRC and 6-bit CRC

-

Supports all types of error detection • Calibration error • Short serial start bit error • Unique pattern error • Nibble minimum length error • Nibble maximum length error • CRC error • Pause length error

-

Supports Sent data frame formats • Two 12-bit fast channels (6 data nibbles) • One 12-bit fast channel (3 data nibbles) • High-speed with one 12-bit fast channel (4 data nibbles, where only values 0-7 are used) • Secure sensor with 12-bit fast channel 1 and secure sensor information on fast channel 2 (6 data nibbles) • Single sensor with 12-bit fast channel 1 and zero value on fast channel 2 (6 data nibbles) • Two fast channels with 14-bit fast channel 1 and 10-bit fast channel 2 (6 data nibbles) • Two fast channels with 16-bit fast channel 1 and 8-bit fast channel 2 (6 data nibbles)

-

Supports interrupt for each error detection and for complete serial message reception

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to microprocessor/microcontroller devices

Deliverables

-

The SAE J2716 Controller interface is available in Source and netlist products.

-

The Source product is delivered in Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()