Description

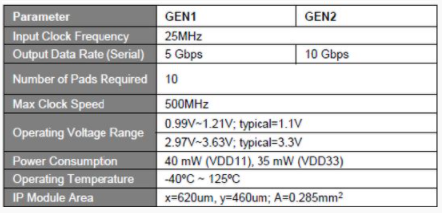

This PHY IP supports both USB 3.2 Gen1 & Gen2. By providing a full on-chip physical transceiver solution with Electro Static Discharge (ESD) protection, an integrated self-test module with built-in jitter injection. This USB 3.2 Gen2 PHY IP implements USB3.2 Gen2 transceiver and can be used as host and device. PHY IP supports USB3.2 Gen2 high speed data rate up to 10Gbps with integrated mixed signal circuit, also supports Gen1 5Gbps data rate.

Features

-

Support PHY interface (PIPE4.3) enables multiple IP sources for USB3 MAC layer

-

Supports 5.0Gbps and 10Gbps serial data transmission rate

-

Supports 16-bit or 32-bit parallel interface

-

Data and clock recovery from serial stream

-

Support 8b/10b encoder/decoder (Gen1), 128/132 encoder/ decoder (Gen2) and error indication

-

Tunable receiver detection to detect worse case cables

-

Low Frequency Periodic Signaling (LFPS) transmission and reception

-

Support SSCG function to reduce EMI effects with tunable down-spread amplitude

-

Selectable TX margining, TX de-emphasis and signal swing values

-

Built-in-self-test with internal Loopback test option

-

Programmable analog circuit parameter adjustment and internal test control

-

Compliant with USB3.2 Gen2 base specification

-

Silicon Proven in TSMC 28HPC+

Deliverables

-

GDSII & layer map

-

Place-Route views (.LEF)

-

Liberty library (.lib)

-

Verilog behavior model

-

Netlist & SDF timing

-

Layout guidelines, application notes

-

LVS/DRC verification reports

-

Test patterns and Test Documentation

![]()