Description

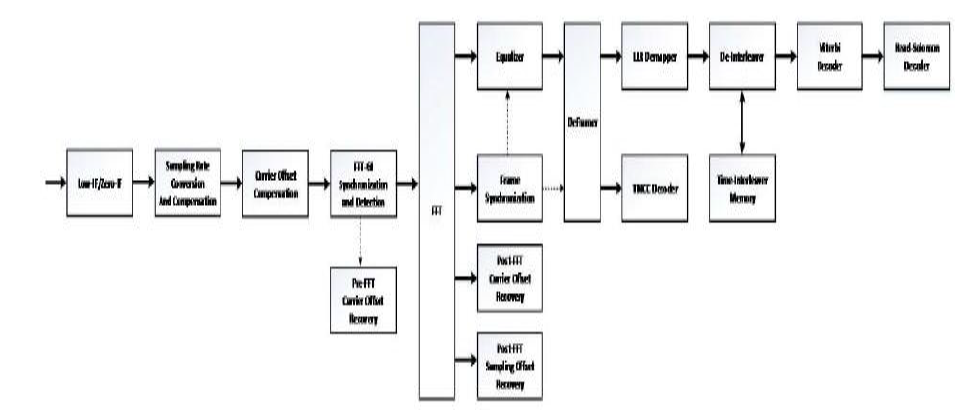

T2M IP has been selling advanced ISDBT/ISDBS3 to Tier-1 Japanese TV makers since 2018. Our team has a deep understanding of the ISDBT standard and also have done a lot of field tests and customer debugs with available Demodulators in the market. Clients ISDBT Demodulator IP is developed based on this experience and also novel patented ideas in the field of algorithm designs. This is a hard core IP with no necessary microcontroller to run any algorithms and is very efficient in terms of power consumption and area. A complete evaluation Xilinx FPGA is available with a 4-weeks lead time and synthesis information in a 22nm process can be made available under NDA.

Features

-

Supports different channel bandwidth: 6MHz,7MHz, 8MHz. Support both ZIF and Low-IF inputs configurations.

-

Digital IF Mixer to support Low-IF from 3MHz to 6MHz with 1Hz precision.

-

Default System Clock 78.125 MHz

-

Default ADC Sampling Rate 19.53125 Msps (System Clock = ADC Sampling Rate x 4) Maximum battery life

-

All the synchronization algorithms are robust at extreme conditions, low CNR down to 0dB CNR or frequency selective Rayleigh fading channels.

-

Ultimate Channel Estimation works for 0dB echo channels up to 90% of Guard Interval size..

-

Very robust sampling clock offset recovery loop working to ±100ppm.

-

Pre-FFT and Post-FFT carrier frequency offset synchronizations supporting carrier frequency offset up to ±1MHz with 1Hz precision.

-

Automatic FFT-GI Detection and Coarse Time Synchronization with outstanding performance at very low SNR down to 0dB as well as 0dB echo channel and Rayleigh fading channels.

-

Very Efficient FFT core supporting 2K,4K, 8K.

-

Ultimate Channel Estimation and Equalization Performance for AWGN, Rayleigh and 0dB Echo Channels (0dB echo channel up to 90% guard interval).

-

Soft Viterbi using LLR demapper to get the best performance.

-

Optimized Time-Interleaver design to minimize the memory area

-

Sampling Rate Conversion supports different ADC sampling-rates without changing system-clock.

-

Support different 3 layer configurations with different segment numbers (Partial/ Differential /Coherent)

-

Integrated TS PID filtering

-

Supports multiple standards and guidelines: ARIB STD-B31 v2,2, ARIB STD-B21 v5.4

-

Optimized Area and Number of Gates

-

Ultra Low Power

![]()