Description

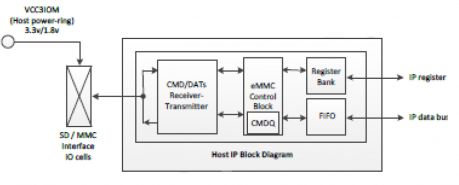

Our Host IP is specially designed to combo both SD eMMC features.

SD feature: The Secure Digital (SD) Card, supports SD5.1 and later specifications, ( A1, Video Speed Class Performance ) It allows the selection of either SD or SPI mode. To store and transfer data securely, the controller provides both data write protection and password protection. The multiple (x1 bit, x4 bit) bus-width feature allows host design flexibility and higher data transfer bandwidth. eMMC feature: The feature of eMMC 5.1 controller is designed based on the JEDEC Standard Specification No.JESD84-B51.

Features

-

SD IP Features :

-

Support SD system specification version 5.1

-

Support Application Performance Class 1.

-

Backward compatible to SD2.0 host

-

Support SD SPI mode

-

Bus Speed Mode (using 4 parallel data lines)

-

Default Speed mode: 3.3V signaling, Frequency up to 25 MHz, up to 12.5 MB/sec

-

High Speed mode: 3.3V signaling, Frequency up to 50 MHz, up to 25 MB/sec

-

SDR12 - SDR up to 25MHz 1.8V signalling

-

SDR25 - SDR up to 50MHz 1.8V signalling

-

SDR50: 1.8V signaling, Frequency up to 100 MHz, up to 50MB/sec

-

SDR104: 1.8V signaling, Frequency up to 208 MHz, up to 104MB/sec

-

DDR50: 1.8V signaling, Frequency up to 50 MHz, Sampled on both clock edges, up to 50MB/sec

-

Switch function command supports Bus Speed Mode, Command System, Drive Strength, and future functions

-

Password Protection of cards (CMD42 - LOCK_UNLOCK)

-

Built-in write protection features (permanent and temporary)

-

Block read and block write supported [class 2 and class 4]

-

Erase supported [class 5]

-

Write protection supported [class 6]

-

Lock card supported [class 7]

-

CPRM(Content Protection for Recordable Media) of SD Card supported

-

eMMC IP Features :

-

Support eMMC specification versions 4.4, 4.41, 4.5, 5.0, 5.01 an 5.1

-

Eleven-wire bus (clock, 1 bit command, 8 bit data bus, and data strobe) and a hardware reset:

-

Clock frequencies of 0-200MHz

-

Three modes of data bus width: 1bit (default), 4bit, and 8bit

-

Support (Alternate) Boot operation mode to provide a simple boot sequence

-

Support SLEEP/AWAKE (CMD5)

-

Host initiated explicit sleep mode for power saving

-

Support block read and write [class 2 and class 4]

-

Support erase [class 5]

-

Support write protection [class 6]

-

Support lock card [class 7]

-

Support High-Speed dual data rate transfer eMMC @ 52MHz 1.8V or 3.3 V I/O

-

Support HS200 single date rate transfer eMMC @ 200MHz 1.8V I/O

Deliverables

-

User Manual

-

Behavior model, and protected RTL codes

-

Synopsys library (LIB)

-

Test patterns and Test Documentation

Benefits

-

Fully Compliant

-

Silicon Proven IP Core

-

In Production in multiple chipsets

![]()