Description

A SOC or ASIC's TileLink component may be intelligently verified with the help of TileLink Verification IP. Version 1.8.1 of the TileLink Specification is fully supported by the TileLink Verification IP. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support TileLink Verification IP. The optional Smart Visual Protocol Debugger for TileLink Verification IP is a GUI-based debugger that speeds up debugging.

Features

-

Compliant with TileLink specification Version 1.8.1.

-

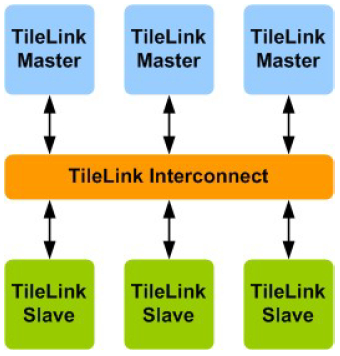

Supports TileLink Master, TileLink Slave, TileLink Interconnect, TileLink Monitor and TileLink Checker.

-

Supports TileLink Uncached Lightweight (TLUL), TileLink Uncached Heavy weight (TL-UH) and TileLink Cached (TL-C) conformance levels.

-

Supports Cache-coherent shared memory.

-

Out-of-order completion support.

-

Burst fragmentation support.

-

Supports all data bus and address field widths.

-

Supports constrained randomization of protocol attributes.

-

Slave, Interconnect and Master support fine grain control of response per address or per transaction.

-

Programmable wait states or delay insertion on different channels. Interconnect has the ability to replicate Master/Slave inserted delays.

-

Ability to inject errors during data transfer.

-

Ability to configure the width of all signals.

-

Programmable Timeout insertion.

-

Supports FIFO memory.

-

Rich set of configuration parameters to control TileLink functionality.

-

On-the-fly protocol and data checking.

-

Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

-

Built in coverage analysis.

-

Callbacks in Master, Slave, Interconnect and Monitor for various events.

-

Status counters for various events on bus.

-

TileLink Verification IP comes with complete testsuite to test every feature of TileLink specification.

Deliverables

-

Complete regression suite containing all the TileLink testcases.

-

Examples showing how to connect various components, and usage of BFM and Monitor.

-

Detailed documentation of all classes, tasks and functions used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()