Description

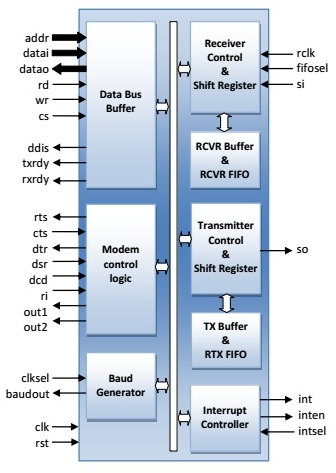

Functionally equivalent to the OX16C950, the D16950 is a soft core for a Universal Asynchronous Receiver/Transmitter (UART). UART and FIFO are the two serial communication modes that are supported. In the FIFO mode, internal FIFOs are turned on, allowing 128 bytes to be stored in both receive and transmit modes (plus 3 bits of error data per byte in the RCVR FIFO). Our effective Core converts data characters received from a peripheral device or MODEM to parallel form before converting data characters from the CPU to serial form. Throughout the functional operation, the CPU has access to the UART's whole state at all times. The kind and state of transfer operations being carried out by the UART, together with any other status information, are given.

Features

-

Software compatible with 16450, 16550,16650,16750 and 16950 UARTs

-

Configuration capability

-

Separate configurable BAUD clock line

-

Majority Voting Logic

-

Two modes of operation: UART mode and FIFO mode

-

In the FIFO mode transmitter and receiver are each buffered with 128 byte FIFO to reduce the number of interrupts presented to the CPU

-

In UART mode receiver and transmitter are double buffered to eliminate a need for precise synchronization between the CPU and serial data

-

Configurable FIFO size up to 512 levels

-

Adds or deletes standard asynchronous communication bits (start, stop and parity) to or from the serial data

-

Independently controlled transmit, receive, line status and data set interrupts

-

False start bit detection

-

16 bit programmable baud generator

-

Independent receiver clock input

-

MODEM control functions (CTS, RTS, DSR, DTR, RI, DCD)

-

Programmable Hardware Flow Control through RTS and CTS

-

Programmable Flow Control using DTR and DSR

-

Programmable in-band Flow Control using XON/XOFF

-

Programmable special characters detection

-

Trigger levels for TX and RX FIFO

-

Interrupts and automatic in-band and out-off-band flow control

-

Fully programmable serial-interface characteristics:

-

5-, 6-, 7-, 8- or 9-bit characters

-

Even, odd, or no-parity bit generation and detection

-

1-, 1.5-, or 2-stop bit generation

-

Internal baud generator

-

Detection of bad data in receiver FIFO

-

Clock prescaler from 1 to 31,875

-

Enhanced isochronous clock option

-

9- bit data mode

-

Software reset

-

Complete status reporting capabilities

-

Line break generation and detection. Internal diagnostic capabilities:

-

Loop-back controls for communications link fault isolation

-

Break, parity, overrun, framing error simulation

-

Full prioritized interrupt system controls

-

Available system interface wrappers:

-

AMBA - APB Bus

-

Altera Avalon Bus

-

Xilinx OPB Bus

-

Fully synthesizable

-

Static synchronous design and no internal tri-states

Deliverables

-

Source code:

-

VHDL Source Code or/and

-

VERILOG Source Code or/and

-

FPGA Netlist

-

VHDL /VERILOG test bench environment

-

Active-HDL automatic simulation macros

-

NCSim automatic simulation macros

-

ModelSim automatic simulation macros

-

Tests with reference responses

-

Technical documentation

-

Installation notes

-

HDL core specification

-

Datasheet

-

Synthesis scripts

-

Example application

-

Technical support

-

IP Core implementation support

-

3 months maintenance

-

Delivery of the IP Core and documentation updates, minor and major versions changes

-

Phone & email support

Applications

-

Serial Data communications applications

-

Modem interface

-

Embedded microprocessor boards

![]()