Description

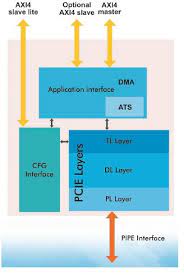

PCIe Gen4 Controller is a configurable and scalable for ASIC and FPGA implementation. The Controller P is compliant with the PCI Express 4.0, and 3.1/3.0 specifications, as well as with the PHY Interface for PCI Express (PIPE) specification and the AMBA® AXI™ Protocol Specification. The IP can be configured to support endpoint, root port, and dual-mode topologies, allowing for a variety of use models, and exposes a configurable, flexible AMBA AXI interconnect interface to the user.

The PCIE Controller IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The PCIE Controller IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with PCI Express 4.0 (32GT/s)

-

3.1(16 GT/s), 3.0(8 GT/s), (16 GT/s), & backward compatible.

-

Compliant with Pipe s.x

-

Supports both PIPE SERDES and non Serdes architecture

-

EPI RCI DMI Switch configurations support architecture

-

Compliant with ATS Specification

-

Compliant with AMBA INTERFACES Latest versions

-

512b Controller architecture and 64B PIPE interface for very high performance

-

Compliant with SR -Iov Specifications.

-

Supports X 16, X8, X4, X2, I Lanes

-

Highly configurable, robust DMA Highly architecture

-

Flexible user interface & AXI4/Native Interfaces

-

LTR, AER, OBFF, MSI, MSI LTR, AER, OBFF, ERC, and Cross link all features supported

-

Required features can be turned on and off at core generation Phase for an optimized gate controller

-

Simple Clocking architecture 32 Physical and 512 virtual functions supported

-

Optional lnbuilt address translator Configurable

-

FPGA validation @ Gen4 speed and loopback mode •

-

@Gen4 speed • PCI SIG compliance test

Benefits

-

Fully compliant, silicon-proven core

-

Comes with Verilog test bench and option to buy full advanced System Verilog Test bench

-

Support directly from engineer who designed the code.

-

Based on RMM (Re Use Methodology Manual guidelines)

-

Supports all the Synthesis tools.

Applications

-

PC

-

Digital TV

-

Set-top boxes

-

Enterprise computing, storage area networks, networking switches, and routers

-

Wireless and mobile devices

-

Industrial, automotive, and IoT

-

Embedded systems

-

Graphics devices

-

Laptops

-

Workstations

-

Servers

Deliverables

-

RTL design in verilog

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with Verilog Test cases.

-

Digital Digital Digital lP controller with UVM VIP counterpart and relatable testbench components and all documentations

-

Hardware validation platforms with full compliance testing support and error scenario support

-

Bit file for digital IP controllers for any type of platforms

![]()