Description

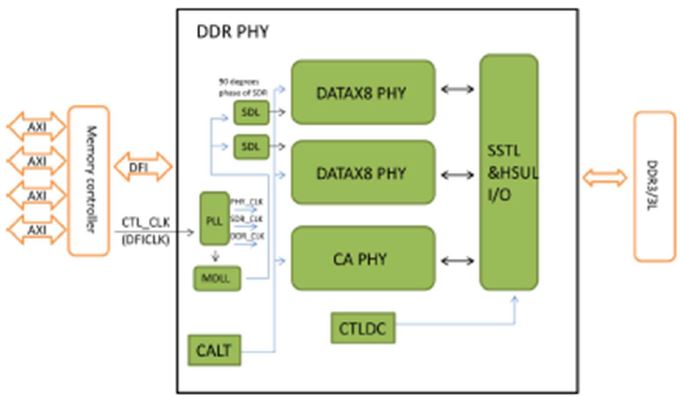

This DDR PHY IP(Double Data Rate) supports DRAM type DDR3, DDR3L this PHY provides low latency, and enables up to 1600Mbps throughput. The DDR IP is compliant with the latest JEDEC standards and is silicon proven. The PHY is optimized for high performance, low latency, low area, low power, ease of integration and faster time-to-market. The DDR (Double Data Rate) controller is used to control DRAM devices as well as to access the data stored on these devices. Provide multiple AXI interface for AXI master and support DFI 2.1 standard for DDR PHY to support DDR3/3L date rate 800~1600 Mbps, X16, dual rank, Write leveling, Data training, low power mode, and standby mode.

Optimized for high performance, low latency, low area, low power, and ease of integration, the DDR4/3 PHY is provided as a hard DDR PHY that is primarily delivered as GDSII including integrated application-specific DDR4/3 I/Os. Supporting the GDSII-based PHY is the RTL-based PHY. The DDR4/3 PHY includes a DFI 2.1 interface to the memory controller and can be combined with controllers for a complete DDR interface solution.

Features

-

Interface: SSTL

-

Maximum controller clock frequency of 400MHz resulting in maximum DRAM data rate of 1600Mbps

-

Data path width scales in 8-bit increment

-

Programmable output impedance

-

Programmable input termination (ODT)

-

Core power:1.1V, I/O power(VDDQ):1.5V/1.35V.

-

ESD : 2KV

-

Support ZQ calibration

-

Support Dual-Rank

-

Support DDR3/3L X16

-

Support write-leveling

-

Operation temperature: -40~125C

-

Support Low power mode, Standby mode and Retention mode

-

Four channel AXI and data width 64/128 bits

-

The shape of the DDR PHY is fixed as I type

Benefits

-

Supports JEDEC standard DDR3, DDR3L and DDR2 SDRAMs

-

High performance DDR PHY supporting data rates from 800 to 1600Mbps

-

GDSII based “hard” PHY avoids timing closure problems common with “soft” RTL-based DDR PHYs

-

Includes application specific DDR I/Os including programmable drive strength and ODT

-

DFI 2.1 compliant controller interface

-

High Utilization

-

Ultra Low Latency

Applications

-

SSD Controllers

-

Automotive

-

Application Processors

-

Digital Baseband Modems

-

Set-Top-Box

-

Digital TV

-

OTT

-

Surveillance

-

IoT, Enterprise

Deliverables

-

User Manual / Application Note

-

Behavior model, and protected RTL codes

-

Protected Post layout netlist and Standard Delay Format (SDF)

-

Synopsys library (LIB)

-

Frame view (LEF)

-

Hspice netlist (SP)

-

Test patterns and Test Documentation

![]()