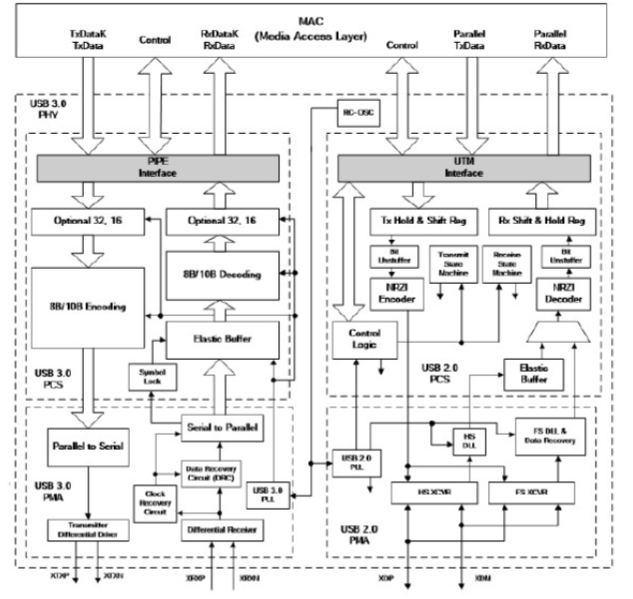

A Universal Serial Bus (USB) transceiver is available for auxiliary devices. The PHY meets with the specifications of USB 3.0 (USB SuperSpeed), USB 2.0 PIPE, and UTMI. Without sacrificing speed or data throughput, the USB3.0 PHY IP transceiver is made to use little power and occupy little space on the chip. To offer complete support for high-performance designs, the USB3.0 PHY IP comprises a full on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, a built-in self-test module with inbuilt jitter injection, and a dynamic equalization circuit. The USB3 MAC layer supports several IP sources across the common PHY interface (PIPE). Utilizing constant power, inbuilt Jitter Injection Output, built-in Self-Test, and authorized changing of analogue circuit characteristics, internal test monitoring and jitter is minimized.

Deliverables

Layer Mapping Information in GDSII Format

Layout Exchange Format for Placement and Routing Visualizations

Standard Cell Characterization Data in Liberty Format

Behavior Modeling in Verilog Syntax

Circuit Connectivity with Timing Details in SDF Format

Layout Design Considerations and Application Recommendations

Reports on Layout Verification for Schematic and Design Rules