Description

The MIPI MPHY Verification IP validates MPHY phy and complies with the MIPI MPHY standard. Experts with experience in developing complicated protocols have created MPHY Verification IP. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support the MIPI MPHY Verification IP. In order to speed up debugging, the MIPI MPHY Verification IP offers an optional Smart Visual Protocol Debugger that is GUI based.

Features

-

Supports 3.0,4.1 and 5.0 MIPI MPHY Specification.

-

Support Type-1 and Type-II operations.

-

Supports both serial and protocol layer interface.

-

Supports all PWM 0-7 gear of operation.

-

Supports all HS 1,2,3,4,5 gear of operation.

-

Serial recovers clock from input serial data stream.

-

Supports clock recovery.

-

Supports disabling of NRZ and PWM for easy serial debugging.

-

Support fine grain control of each timing parameter.

-

Support timing checks to validate each timing period.

-

Support programmable sync pattern and length.

-

Support programmable adapt pattern and length.

-

Support following 8b/10b error insertion and detection, • Invalid K character injection • Injection of disparity errors • Wrong K character injection • Corruption of Marker characters

-

Supports periodic Filler (NOP) insertion.

-

Supports periodic Marker 1 insertion.

-

Supports periodic fixed pattern sending to verify MPHY support for PCI Express, Unipro.

-

Supports inband reset signaling and detection.

-

Supports Test Pattern generation and checking (CJTPAT and CRPAT).

-

Supports Inter lane skew insertion and detection.

-

Supports glitch detection.

-

MPHY Receiver models clock recovery and jitter compensation.

-

Monitor, Detects and notifies the testbench of all protocol and timing errors.

-

Status counters for various events in bus.

-

Callbacks in transmitter and receiver for various events.

-

MIPI MPHY Verification IP comes with complete test suite to test every feature of MIPI MPHY specification.

-

Supported below latest version 5.0 features • Supports PWM G1 in LS mode and HSG1 - HSG5 gear in HS mode. Remaining PWM gears are removed • Supports Line Reset followed with either HS mode(HS G1A or HS G1B) or LS mode(PWM G1) • Extended RMMI symbol Bus Width as 80bits,160bits • Removed Line-cfg state • Supports Eye monitor

Deliverables

-

Complete regression suite containing all the MIPI MPHY testcases.

-

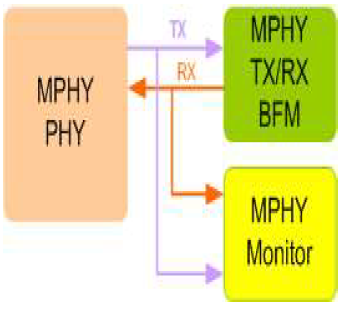

Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()