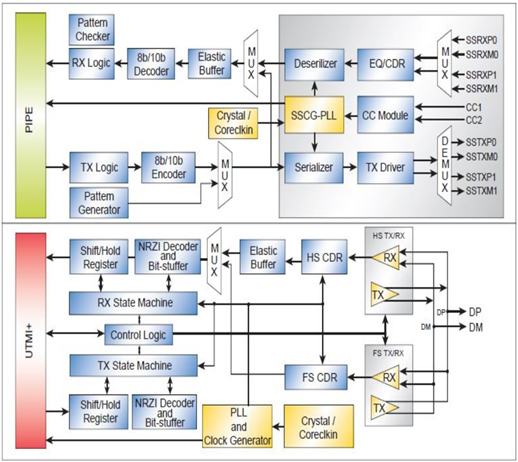

The USB 3.2 Gen2X1 transceiver IP supports all USB 3.2 Gen2X1 host and peripheral applications up to 10Gbps. It conforms with the standards of UTMI+ and PIPE4.0. The USB 3.2 Gen2X1 IP features high-speed mixed signal circuits to support Gen2 and Gen1 traffic and is backward compatible with high-speed data rates of 480Mbps, full-speed data rates of 12Mbps, and low-speed data rates of 1.5Mbps. The USB 3.2 Gen2X1 IP provides an active switch to enable bi-directional plug-in and particular functionality (such VBUS setup and USB attachment cable orientation detection) through the CC1/CC2 pins specified in the Type-C connection in order to support the USB Type-C connector.

Deliverables

Physical Layout Representation with Layer Information in GDS2 .

LEF File Containing Placement and Routing Details .

lib File with Timing and Power Data

Verilog Behavioral Model

SDF-Annotated Netlist

Layout Specifications and Application Insights

LVS and DRC Verification Results