Description

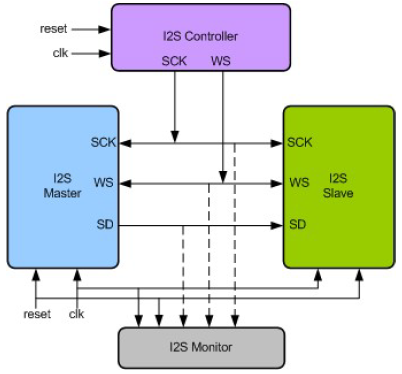

I2S Verification IP provides an smart way to verify the I2S bi-directional two-wire bus. The I2S Verification IP is fully compliant with version Philip's I2S-Bus Specification June 5, 1996 and provides the following features. I2S Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env I2S Verification IP comes with optional Smart Visual Protocol Debugger which is GUI based debugger to speed up debugging.

Features

-

Complies with Philips I2S Specification June 5, 1996

-

Full I2S Transmitter, Receiver and Controller functionality

-

Supports up to 32 channels in transmit path

-

Supports up to 32 channels in receive path

-

Supports programmable word length 8, 12, 16, 20, 24, 32

-

Supports programmable padding

-

Supports programmable bit reversal

-

Supports left and right justified

-

Both transmitter and receiver can either work with SCK as input or can drive SCK

-

Supports programmable data rate on transmit path • Can operate as master or slave in several configurations • Master or slave mode as transmitter • Master or slave mode as receiver • Master mode as controller (does not transmit or receive data) • Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

-

Status counters for various events on bus.

-

Callbacks in transmitter, receiver and monitor for various events.

-

Supports constraints Randomization.

-

Built in functional coverage analysis.

-

I2S Verification IP comes with complete test suite to test every feature of I2S specification.

Deliverables

-

Complete regression suite containing all the I2S testcases.

-

Examples showing how to connect various components, and usage of Master, Slave and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()