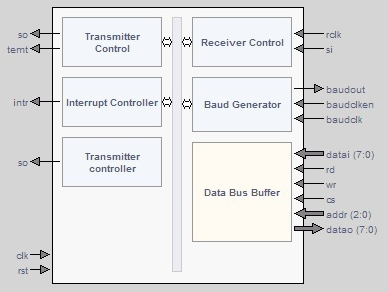

Description

The Octal UART Core software for the D2698 is compatible with the SC2698. The three character receiver FIFO, increased baud rate, and configurable receiver and transmitter interrupts are all parts of the core. Two full-duplex asynchronous receiver/transmitter channels are offered by the D2698 Octal Universal Asynchronous Receiver/Transmitter (DUART), a communications tool. It offers a modem interface and directly connects to microprocessors. It may be utilized in polled or interrupt-driven systems. Each channel can have its own separate programming for its operating mode and data type. Also available are 26 fixed baud rates, a 16X clock generated by a programmable counter/timer, and an external 1X or 16X clock. Each receiver and transmitter can choose one of these options for their working speed. Using an external power source, the baud rate generator and counter/timer.

Features

-

Software compatible with SCC2698 UART

-

Configuration capability

-

8 full-duplex independent asynchronous receiver/transmitters

-

3 character FIFOs for each receiver channel

-

Programmable data format:

-

5 to 8 data bits plus parity

-

Odd, even, no parity or force parity

-

1, 1.5 or 2 stop bits programmable in 1/16-bit increments

-

16-bit programmable Counter/Timer

-

Programmable baud rate for each receiver and transmitter selectable from:

-

26 fixed rates: 50 to 115.2k baud

-

Programmable user-defined rates derived from a programmable counter/timer

-

External 1X or 16X clock

-

Parity, framing, and overrun error detection

-

False start bit detection

-

Line break detection and generation

-

Programmable channel mode:

-

Normal (full-duplex)

-

Automatic echo

-

Local loopback

-

Remote loopback

-

2 Multi-function input and 2 I/O ports:

-

Can serve as clock, modem, or control inputs

-

Change of state detection on four inputs

-

Multi-function output port:

-

Individual bit set/reset capability

-

Outputs can be programmed to be status/interrupt signals

-

FIFO states for DMA and modem interface

-

Versatile interrupt system:

-

Single interrupt output with eight maskable interrupting conditions

-

Output port can be configured to provide a total of up to six separate wire-ORable interrupt outputs

-

Each FIFO can be programmed for four different interrupt levels

-

Watchdog timer for each receiver

-

Maximum data transfer rates: 1X – 1Mb/sec, 16X – 1Mb/sec

-

Start-end break interrupt/status

-

Detects break which originates in the middle of a character

-

Power down mode

-

Receiver timeout mode

Deliverables

-

Source code:

-

VHDL Source Code or/and

-

VERILOG Source Code or/and

-

FPGA Netlist

-

VHDL /VERILOG test bench environment

-

Active-HDL automatic simulation macros

-

NCSim automatic simulation macros

-

ModelSim automatic simulation macros

-

Tests with reference responses

-

Technical documentation

-

Installation notes

-

HDL core specification

-

Datasheet

-

Synthesis scripts

-

Example application

-

Technical support

-

IP Core implementation support

-

3 months maintenance

-

Delivery of the IP Core and documentation updates, minor and major versions changes

-

Phone & email support

Applications

-

Serial Data communications applications

-

Modem interface

-

Embedded microprocessor boards

![]()