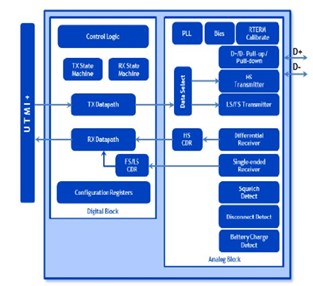

The entire physical layer (PHY) IP solution for USB 2.0 was created to provide exceptional performance and consume little power. The USB2.0 IP implements the High-Speed USB 2.0 Transceiver, which can be used with hosts, devices, or OTG function controllers. The specification that follows UTMI+level 3 is the USB2.0 PHY IP, which supports Full-Speed (12 Mbps) and Low-Speed (1.5 Mbps) data rates. By merging numerous mixed-signal circuits, high-speed data transfer @ 480Mbps can be accomplished. The expanded USB Battery Charging standards, intended for usage in consumer electronics and mobile devices, are also supported by the USB2.0 PHY IP. The USB 2.0 PHY IP standard is implemented by numerous factories and nodes, including "TSMC 28HPC+, TSMC 40LP, TSMC 40LL, UMC 28HPC, UMC 40LP, UMC 55SP, UMC 55EF, SMIC 14SF+, SMIC 40LL, SMIC 55LL." The USB2.0 PHY IP transceiver's small chip size and low power consumption had no impact on performance or data throughput. In order to fully allow host and device functionality, the USB2.0 PHY IP delivers a full on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, a clock generating block provided by an internal PLL, and a resistor termination calibration circuit.

Compliant with USB2.0 and USB1.1 specification

Compliant with UTMI Specification Version level 3.

Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

16-bit, 30MHz or 8-bit, 60MHz parallel interface for HS/FS

Serializing for transmitting data stream and Deserializing for receiving data stream

USB Data Recovery and Clock Recovery on receiving

Integrated Bit Stuffing and NRZI encoding for Transmit

Integrated Bit Un-Stuffing and NRZI decoding for Receive

SYNC and EOP generation on transmit packets and detection on receive packets

Internal reference resistor that replaces the external reference resistor

Built in self test for production testing

Supports USB suspend state and remote wakeup

Supports detection of USB reset, suspend and resume signaling

Supports high speed identification and detection as defined by USB 2.0 Specification

Support high speed host disconnection detection

Silicon Proven in TSMC 28nm, TSMC 40nm, UMC 28nm, UMC 40nm, UMC 55nm, SMIC 14nm, SMIC 40nm, SMIC 55nm

Silicon Proven in TSMC 16FFC.

Deliverables

GDSII Physical Layout Representation with Layer Mapping

Representation of Placement and Routing Topology in .LEF

Repository of Timing and Power Models in Liberty Format

Functional Simulation Model in Verilog Language

SDF Timing Specifications Integrated into Circuit Connectivity Data

Guidelines for Successful Layout Construction and Compliance

Verification Reports Confirming Layout Schematic and Rule Conformance