Description

USB 3.0 Verification IP provides a smart way to verify the USB 3.0 component of a SOC or an ASIC. The USB 3.0 Verification IP is fully compliant with standard USB Specification 3.0. The USB 3.0 VIP can be readily customized and optimized for a wide range of specific system applications. USB 3.0 Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env. USB 3.0 Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Features

-

Compliant with USB 3.0 specification

-

Supports Superspeed USB 3.0 and 3.0 OTG

-

Complete solution for thorough chip-level verification

-

Comprehensive model support a Host, Device, Hub, PHY

-

Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

-

Supports constrained randomization of protocol attributes

-

Supports all types of error injection and detection

-

Supports error injection in all the layers of USB 3.0

-

Configurable PHY Interface width 8, 16 or 32 bits

-

PHY interface supports data scrambling to reduce EMI emissions

-

Comprehensive compliance testsuite for Protocol, Link, and Physical layer verification

-

Supports Low frequency periodic signaling (LFPS) for initialization and power management (U1, U2 & U3)

-

Supports Interrupt/Bulk/Isochronous/Control Transfers

-

Control transfers supported by Endpoint 0

-

Separate Endpoint Buffers for IN bound and OUT bound packets

-

Supports for USB 3.0 low power states

-

Bulk Stream support

-

Supports Lane polarity inversion

-

Supports eXtensible Host Controller Interface

-

Compliant with USB 3.0 specification.

-

Compliant with USB 3.0 Super speed Inter chip supplement 1.0.

-

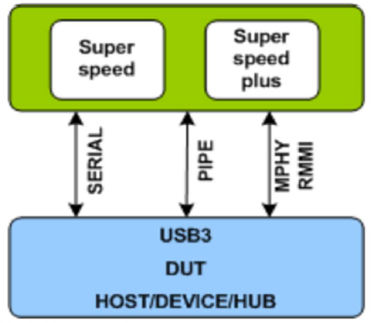

USB 3.0 host and device with SERIAL/PIPE/SSIC interfaces

-

Supports dual-simplex, four-wire differential signaling and 8b/10b parallel interface

-

Operates at Super speed (5 Gbit/s), High(480 Mbit/s) or Full speed(12 Mbit/s) modes

-

Supports SS-OTG,SSPC-OTG Devices,SS-PO Devices and SS-EH Devices

-

Supports ADP,HNP,SRP and RSP

-

USB 3.0 host and device with SERIAL/PIPE/SSIC interfaces

-

Supports Inter-Chip Supplement to the USB Revision 3.0 Specification (Super Speed Inter-Chip) using MIPI MPHY

Deliverables

-

Complete regression suite containing all the USB 3.0 testcases.

-

Examples showing how to connect various components, and usage of BFM and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()