Description

The CPRI Verification IP checks CPRI interfaces and is completely compatible with CPRI Specification V4.2/V5.0/V6.0/V6.1 and V7.0. It comes with a comprehensive test suite that covers the majority of potential scenarios. It executes all conceivable protocol tests in a guided or highly randomized manner, adding the opportunity to generate the greatest number of situations to successfully check the DUT. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support CPRI Verification IP. In order to speed up debugging, CPRI Verification IP offers an optional Smart Visual Protocol Debugger that is GUI based.

Features

-

Compliant with CPRI Specification V4.2/V5.0/V6.0/V6.1/V7.0

-

Supports the Physical link layer (Layer 1) of the CPRI specification.

-

Supports different standard line bit rates of the CPRIspecification • 614.4 MBPS, 1228.8 MBPS • 2457.6 MBPS, 3072.0 MBPS • 4915.2 MBPS, 6144.0 MBPS • 8110.08 MBPS, 9830.4 MBPS • 12165.12 MBPS, 24330.24 MBPS

-

Supports disparity and invalid code insertion in 8B/10B.

-

Supports 8B/10B line coding for bit rates upto 9830.4 MBPS

-

Supports 64B/66B line coding without RS-FEC for 8110.08, 10137.6, 12165.12 and 24330.24 bit rates

-

Supports 64B/66B line coding with RS-FEC for 24330.24 MBPS bit rate • RS-FEC with alignment marker and without scrambler support • RS-FEC without alignment marker and with scrambler support • RS-FEC without alignment marker and without scrambler support

-

Provides an 8-bit, 16-bit, or 32-bit for IQ data

-

Performs subchannel mapping:

-

Supports a slow C&M channel based on a serial HDLC interface at following standard HDLC bit rates • 240 KBPS, 480 KBPS, 960 KBPS • 1920 KBPS, 2400 KBPS, 3840 KBPS • 4800 KBPS, 7680 KBPS

-

Provides a start-up sequence state machine in hardware for both REC and RE nodes which performs:

-

L1 Synchronization, Protocol setup

-

C&M Plane setup, Supports Link Maintenance

-

LOS detection, LOF detection

-

RAI indication, SDI indication

-

Detects and reports the following errors • Invalid control character • Invalid data character, Scrambler errors • Disparity errors • Invalid 10bit code group errors

-

Undersize and oversize frame errors

-

CRC errors, Framing errors, LOS and LOF errors

-

Glitch insertion and detection.

-

CPRI Verification IP comes with complete test suite to test every feature of CPRI specification

Deliverables

-

Complete regression suite containing all the CPRI testcases.

-

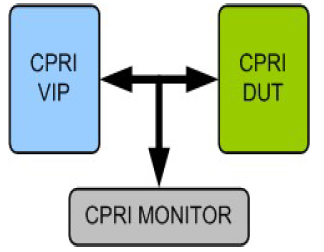

Examples showing how to connect various components, and usage of Master, Slave and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation contains User's Guide and Release notes

![]()