Description

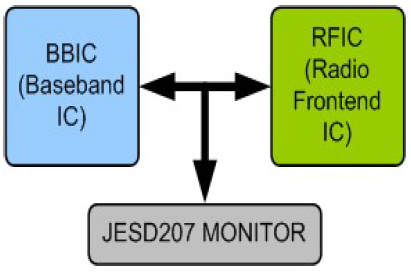

The Radio Front end-Baseband digital parallel interface is verified by JESD207. The following functionalities are offered by JESD207 Verification IP, which may be used to verify BBIC or RFIC that adheres to the JESD207 basic protocol as described in JESD207. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support JESD207 Verification IP. The Smart Visual Protocol Debugger (Smart ViPDebug), a GUI-based debugger that speeds up debugging, is an optional addition to the JESD207 Verification IP.

Features

-

Supports JESD207 specification.

-

Operates as BBIC (Baseband IC) and RFIC (Radio front end IC) monitor.

-

Supports half duplex data transfer.

-

Supports DDR source synchronous data transfer timing.

-

Supports both data path transaction and control plane transactions.

-

Supports multiple parallel sample streams in BBIC and RFIC data path interface.

-

Supports data path transaction • Supports transmit burst and receive burst • Supports both 10 bits and 12 bits sample width • Supports 2 way interleave and 4 way interleave transactions • Supports 1T1R,1T2R,2T2R systems

-

Supports control plane transaction • Supports 4 wires write and 4 wires read • Supports 3 wires write and 3 wires read • 1bit command plus 7bit address control field format • Serial clock can be stopped between transactions for reducing control plane power consumption to negligible levels • Extended data transactions

-

Supports various kinds of errors • Mixed data error • Invalid address error

-

Status counters for various events on bus.

-

Supports constraints randomization.

-

Built in functional coverage analysis.

-

Call-backs in BBIC and RFIC for various events.

-

Test suite to test each and every feature of JESD207 specification.

Deliverables

-

Complete regression suite containing all the JESD207 testcases to certify JESD207 Slave/Master device

-

Examples showing how to connect various components and usage of Master, Slave and Monitor.

-

Detailed documentation of all class, task and functions used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()