Description

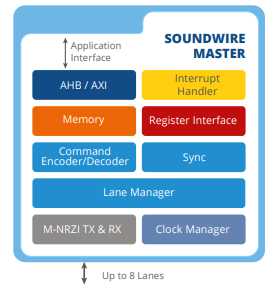

The MIPI SoundWire is an interface specification that enables bidirectional digital audio communication between a master and one or more slave devices, or among only slave devices. It is optimized for mobile and ‘mobile-inspired’ systems. It can coexist with MIPI-compliant and non MIPI-compliant devices alike. MIPI SoundWire is low-complex, low-power, and low-latency interface that supports multi-channel data. Being low gate count allows it to be incorporated it into smaller components, like microphones and amplifiers. SoundWire Master is used in master controllers like amplifiers or processors, transferring or receiving audio data from a SoundWire slave, like the one connected to a microphone or a speaker. Similarly, SoundWire Slave is a SoundWire standard-compliant slave, supporting slave to slave communication, depending on the device component connected.

Features

-

Compliant with MIPI SoundWire Standard 1.1x

-

SoundWire Host can support up to 11 Slaves

-

Support up to 8 data lanes

-

Support for slave-to-slave transfers

-

Modified-NRZI data encoding

-

Special internal register space for each device

-

Optional monitor interface

-

Optional APB/AXI interface support

-

Configurable data width: 8/16/32-bit

Deliverables

-

Configurable RTL Code

-

HDL based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers and performance monitors

-

Configurable synthesis shell

-

Documentation

-

Design Guide

-

Verification Guide

-

Synthesis Guide

Benefits

-

PDI count, width, & type

-

Application interface – APB or AXI

-

Command FIFO depth

-

Data lane count

-

Data port memories

-

Highly modular and configurable design

-

Layered architecture

-

Supports both sync and async reset

-

Clearly de-marked clock domains

-

Extensive clock gating support

-

Multiple Power Well Support

-

Software control for key features

![]()