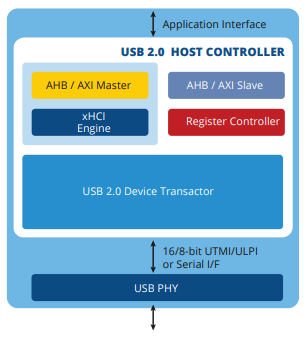

We provide highly configurable and scalable USB 2.0 host/ device/dual-mode controller IP Cores for a wide range of applications. The USB 2.0 controller is designed for compliance with USB2.0 specification Revision 1.0 and all associated ECN’s. The USB 2.0 host controller is architected to optionally include a high-performance DMA engine, based on xHCI specifications. All buffering associated with the DMA Engine are configurable, based on latency and performance requirements. The core can be configured to support full-fledged xHCI implementations for use in standard PCIe-USB bus adaptors/chipsets.

It can also be configured with a subset of features for embedded applications requiring limited host functionality. The USB 2.0 host controller is based on xHCI specifications and can be used in any OS that provides xHCI/USB Stacks, such as Android, Linux, and Windows. The USB 2.0 host controller exposes an AXI or AHB Master interface for the data-path, and an AHB slave interface for register access. Optionally, an interoperate-proven third party PCIe-AXI/AHB bridge is also provided for use in standard desktop/server applications. Further, the controller can be provided with no xHCI Engine and no buffering, operating in a cut-through mode, forwarding and receiving USB payloads, and managing only the USB protocol. In this case, the customer may implement their own differentiated DMA Engine. A simple transmit and receive buffer is included in this configuration, accessible by software over the slave register access interface (typically AHB). This results in very-low-footprint hardware, ideal for cases where the software can completely manage USB traffic – such as sequencing of USB transactions.

Adaptable RTL Code

HDL Test Environment with Behavioral Models

Test Case Compilation

Protocol Compliance Verification, Bus Monitoring, and Performance Analysis

Configurable Synthesis Framework

Design Guidebook

Verification Handbook

Synthesis Process Manual

FPGA Validation Platform for Pre-Tape-out Testing

Reference Firmware Implementation and Documentation