Description

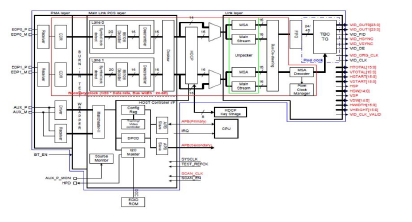

This Display Port v1.4 Rx PHY IP Core supports Channel capacity, offering programmable analog characteristics like CDR Bandwidth, Equalizer Strength, Terminator Resistor, and BGR Voltage, up to 5.4 Gbps per channel (HBR2). It also includes testability options such as PLL alone test and analog signal monitor, ensuring comprehensive functionality for signal processing and testing in digital display systems.

Features

-

DisplayPort version 1.4 compliant receiver

-

PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

-

Integrated 100-ohm termination resistors with common-mode biasing

-

Integrated equalizer with tunable strength

-

eDP version 1.4a / DP version 1.3 compliant

-

receiver Supports HDCP1.4 and HDCP2.2(Optional)

-

Consists of configurable (4/2/1) link channels and one AUX channel

-

Supports 1.62Gbps (RBR), 5.4Gbps (HBR2) and 8.1 Gbps (HBR3) bit rate

-

Supports main link operation with 1 or 2 or 4 lanes

-

Supports both Default and Enhanced Framing Mode Supports SST mode

-

Supports video packet and audio packet

-

Supports 18 / 24-bit RGB digital video output format Master I2C interface for DDC connection

-

Interface to external HDCP key storage

-

Configuration registers programmable via AMBA interface

-

Configurable analog characteristics

-

CDR bandwidth

-

Equalizer strength

-

Terminator resistance

-

BGR voltage

-

Regulator voltage

-

Support PLL test and internal analog signal monitor

-

1.8V/0.9V power supply

-

Silicon Proven in TSMC 40nm LP.

Deliverables

-

Verilog RTL or netlist source code of LINK controller.

-

Abstracted timing models for synthesis and STA

-

Timing constrains for synthesis and physical layout

-

Behavioral Verilog Model, simulation test bench, run control scripts, and test stimuli

-

Physical design database

-

Integration guidelines

-

Reference software sample code

![]()