Description

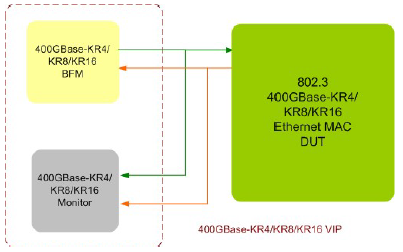

The 400GBase-KR4/KR8/KR16 Ethernet Verification IP validates the MAC-to-PHY layer interfaces of designs having a 400GBase-KR4/KR8/KR16 Ethernet interface in accordance with IEEE 802.3bs requirements. It can operate in environments that use SystemVerilog, Vera, SystemC, E, and Verilog HDL. Experts in Ethernet who have created Ethernet solutions for firms like Intel, Cortina-Systems, Emulex, and Cisco are behind the development of 400GBase-KR4/KR8/KR16 verification IP. We are conscious of the procedures required for verifying an Ethernet product. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and nonstandard verification environments all natively support 400GBase-KR4/KR8/KR16 Verification IP. An optional Smart Visual Protocol Debugger (Smart ViPDebug), a GUI-based debugger to expedite debugging, is included with the 400GBase-KR4/KR8/KR16 Verification IP.

Features

-

Supports scrambler

-

Supports FEC

-

Supports backplane auto-negotation

-

Supports CDR for serial protocols

-

Supports MDIO slave and master model as per Clause 22 and Clause 45

-

Supports Glitch insertion and detection

-

Supports Pause frame generation and detection.

-

Supports all types of 50GBase-KR/KR2 TX and RX errors insertion/detection. • Oversize, undersize, inrange, out of range Packet size errors • Missing SPD/EPD/SFD framing errors • SFD on wrong lane • CRC Error • Lane skew insertion • Invalid /D/ and /K/ character injection • Variable preamble and IPG insertion • Invalid block code insertion • Sync bit corruption • FEC error injection • Scrambler error injection

-

Comes with 50GBase-KR/KR2 Tx BFM, 50GBase- KR/KR2 Rx BFM, and 50GBase-KR/KR2 PCS Monitor

-

Monitor supports detection of all protocol violations.

-

Built in coverage analysis.

-

Callbacks in master and slave for various events

-

Status counters for various events in bus

Deliverables

-

Complete regression suite containing all the testcases.

-

Examples showing how to connect various components, and usage of TXRX BFM and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes.

![]()