Description

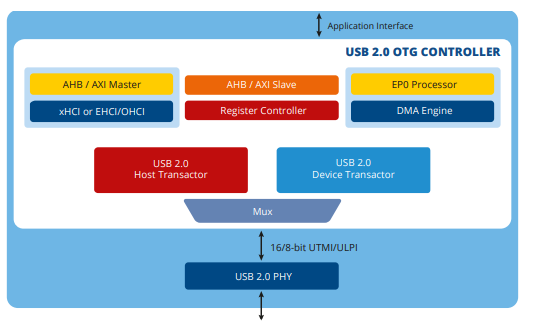

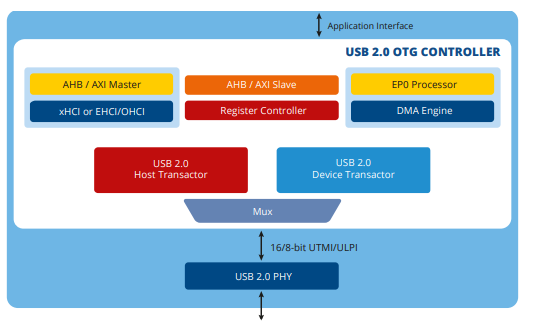

Our company offers a highly configurable and adaptable USB 2.0 OTG controller IP core, suitable for a wide range of applications. This controller adheres to the latest industry standards (USB 2.0 and USB OTG) and works seamlessly with existing Windows, Linux, and Android drivers in host mode, minimizing software development effort and risks. It boasts multiple interface options for various systems and offers the flexibility to connect single devices directly or manage multiple devices via hubs. Additionally, optional features like a high-performance DMA engine and a dedicated processor block can be included to optimize performance and reduce development time in device mode. Overall, this versatile controller empowers developers with a wide range of functionalities and customization options, catering to both basic and advanced needs.

Features

-

The USB 2.0 OTG controller can be configured to support all types of USB transfers – bulk, interrupt and isochronous. In device mode, it can be dynamically configured to support a configurable number of endpoints, interfaces, alternate interfaces, and settings.

-

The USB 2.0 OTG controller can be configured to support any combination of USB 2.0 interface speeds – LS (1.5 Mbps), FS (12.0 Mbps), HS (480 Mbps). Sample combinations are LS only, FS only, HS only, LS and FS only, or FS and HS only.

-

The USB 2.0 OTG controller has full support for all low power features of USB specifications, supporting suspend, remote wakeup and Link Power Management states – L1, L2.

-

The USB 2.0 OTG controller has full support for all test modes features which is required for obtaining USB-IF certification.

-

The USB 2.0 OTG controller has full support for OTG features such as SRP, HNP and ADP along with software configurable options to turn these features on/off.

-

Our USB controllers have been silicon proven in a wide range of products such as graphics controller, flash storage controllers, SATA bridges with support for bulk streaming, embedded hosts, docking stations, mobile application processors, smart TV, or hubs.

Benefits

-

Highly modular and configurable design

-

Layered architecture

-

Fully-synchronous design

-

Support for both sync and async reset

-

Clearly demarcated clock domains

-

Extensive clock gating support

-

Multiple power well support

-

Software control for key features

Applications

-

Graphics controller

-

Flash storage controller

-

SATA bridges with support for bulk streaming

-

Embedded hosts

-

Docking stations

-

Mobile application processors

-

Smart TV

-

Hubs

Deliverables

-

Configurable RTL Code

-

HDL-based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers, and performance monitors

-

Configurable synthesis shell

-

Design guide

-

Verification guide

-

Synthesis guide

-

FPGA platform for pre-tape-out validation

-

Reference firmware