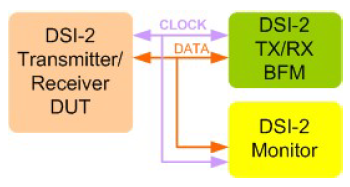

Description

The MIPI DSI-2 bi-directional two-wire/three-wire bus may be verified in an intelligent fashion thanks to the MIPI DSI-2 Verification IP. The MIPI DSI-2 Verification IP offers the following characteristics and is completely compatible with the serial interface version 2.0 MIPI Alliance specification. System Verilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and nonstandard verification environments all natively support the MIPI DSI-2 Verification IP. The optional Smart Visual Protocol Debugger, a GUI-based debugger to speed up debugging, is also included with the MIPI DSI-2 Verification IP.

Features

-

Full MIPI DSI-2 Tx and Rx functionality.

-

Supports 2.0 MIPI DSI-2 Specification.

-

Support both DPHY and CPHY

-

Supports MIPI DBI specification

-

Supports MIPI DCS specification

-

Supports all types of D-PHY, C-PHY short packets

-

Supports all types of D-PHY, C-PHY long packets

-

Supports all lane configuration

-

Supports 8 lane configuration of DPHY layer

-

Supports 4 lane configuration of CPHY layer

-

Supports multiple packets per transmission

-

Supports differential and single ended mode of operation

-

Supports PPI interface

-

Supports all BTA commands

-

Supports Link Distribution Function

-

Supports skew calibration, data scrambling

-

Supports below data rates in DPHY layer • 80 to 1500 Mbps per lane without deskew calibration • Upto 2500Mbps per lane with deskew calibration • Upto 12000Mbps per lane with equalization

-

Supports below data rates in CPHY layer • 17.1 Gbps for 3 lanes • 5.7 Gbps for 1 lane

-

Supports Display Stream Compression (DSC)

-

Various kind of Tx and Rx errors generation andetection • SoT error, Sync error, Word count error, Sync length error, Checksum error, ECC error

-

Supports detection of all timeouts and injection of various timeout errors

-

Supports both high speed and low power packet transmission and reception

-

Supports fine grain control of timing parameters

-

Status counters for various events in bus.

-

Operates as a Tx, Rx, or both.

-

Monitor, Detects and notifies the testbench of all protocol and timing errors.

-

Callbacks in node transmitter, receiver and monitor for user processing of data.

-

MIPI DSI-2 Verification IP comes with complete test suite to test every feature of MIPI DSI-2 specification.

-

Functional coverage for complete MIPI DSI-2 features

Deliverables

-

Complete regression suite containing all the MIPI DSI-2 testcases.

-

Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes.

![]()