Description

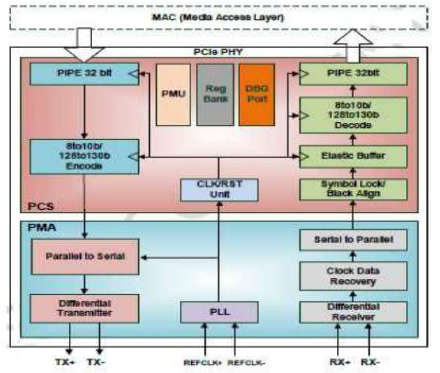

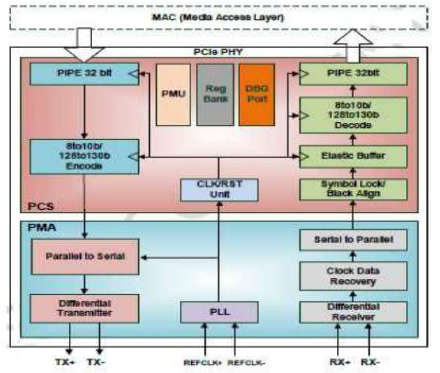

This Peripheral Component Interconnect Express (PCIe) x4 PHY is compliant with PCIe 4.0 Base Specification with support of PIPE 4.4 interface spec. Lower power consumption is achieved due to support of additional PLL control, reference clock control, and embedded power gating control. Also, since a fore mentioned low power mode setting is configurable, the PHY is widely applicable for various scenarios under different consideration of power consumption.

Features

-

Compliant with PCIe 4.0 Base Specification

-

Compliant with PIPE 4.4

-

Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

-

Supported physical lane width: x4

-

Supported parallel interface: 32-bit

-

Supported input reference clock: 100 MHz

-

Supported parallel interface data clock: 62.5 MHz, 125 MHz and 250 MHz and 500MHz

-

Supporting low power operation with configurable setting in power state P1/P2/L1 PM Substates: PLL control, reference clock control, and embedded power gating control

-

TSMC 12nm FFC 1P9M_2Xa1Xd3Xe2Z_Al=28KA (ULVT/SVT) process

-

Operating Voltage: 0.8V and 1.2V

-

Providing robust testability by low-cost Build-In Self-Test (BIST) via near-end analog and external loopback interface as well as far-end analog/digital loopback interface

Deliverables

-

Application Note / User Manual

-

Behavior model, and protected RTL codes

-

Protected Post layout netlist and Standard Delay Format (SDF)

-

Synopsys library (LIB)

-

Frame view (LEF)

-

Metal GDS (GDSII)

-

Test patterns and Test Documentation