Description

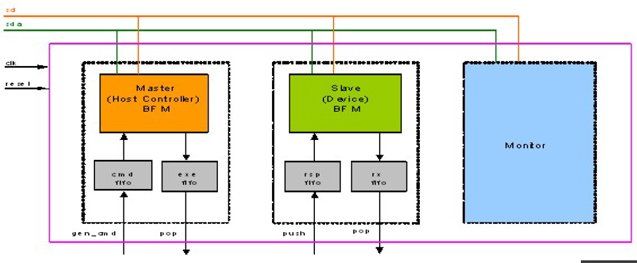

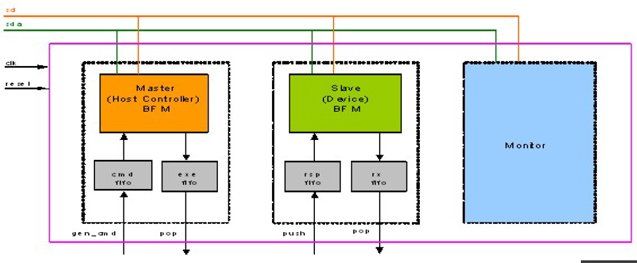

The Verification IP (VIP) for JESD403 provides an efficient and simple way to verify the JESD403 bidirectional two-wire serial interface. The VIP is fully compliant with version 1.0 specifications. JESD403 VIP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env JESD403 VIP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Features

-

Compliant with JESD403 version 1.0 specification.

-

Full JESD403 Host Controller and Device functionality.

-

Two wire serial interfaces up to 12.5 MHz.

-

Supports Dynamic Address Assignment including Static Addressing for legacy I2C Devices.

-

In-Band Interrupt support.

-

Support for all JESD403 Common Command Codes (CCC's).

-

7-bit configurable Slave Address.

-

Supports HOST DEVICE ADDRESS.

-

Supports Timed reset.

-

Supports Write/Read formats.

-

Supports PEC enable/disable.

-

Master SCL clock stalling is supported.

-

Slave supports control of response fields including NACK, Data and Slave busy.

-

Supports slave error types S1 and S2.

-

Supports injection of various errors. • Master aborting in middle of access • Master doing ACK on last read access

-

Call-backs in Master, Slave and Monitor for user processing of data

-

Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

-

Functional coverage of complete JESD403 specs.

-

JESD403 Verification IP comes with complete testsuite to test every feature of JESD403 specification.

Deliverables

-

Complete regression suite containing all the JESD403 testcases to certify JESD403 Slave/Master device

-

Examples showing how to connect various components and usage of Master, Slave and Monitor.

-

Detailed documentation of all class, task and functions used in verification env.

-

Documentation also contains User's Guide and Release notes