Description

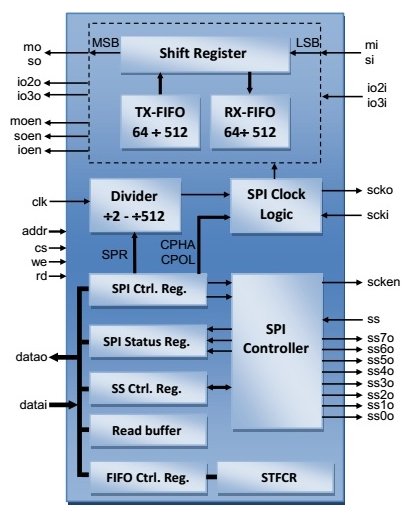

The SPI is a fully programmable SINGLE, DUAL, or QUAD SPI master/slave device that enables users to modify the polarity and phase of the serial clock signal SCK. The Hyper BusTM specification, xSPI (Expanded Serial Peripheral Interface - JESD251A) specification, and XccelaTM Bus Interface are all completely compatible with the SPI controller. The SPI Controller makes it simple to communicate with the majority of SPI FLASH memory on the market. Information shifting and sampling on serial data lines are synchronized via a serial clock line (SCK). It is a design that can be used in a range of process technologies since it is technology neutral. The SPI system is flexible enough to interact with a wide variety of peripherals from various vendors directly. The option of two essentially distinct clock polarities and two fundamentally different.

Features

-

Set of software accessible control registers to execute any Flash memory command

-

Supports any device clock frequency, polarity and phase,

-

Programmable baud rate generator,

-

Built in FLASH Commands decoder supports most popular FLASH devices,

-

Optional built in AES Encoder/Decoder

-

DMA support

-

Support for various SPI Bus Standards: Hyper BusTM, xSPI, XccelaTM

-

Compliant with AMBA2 Specification, supports APB, AHB, AXI bus interfaces

-

Single, Dual, Quad SPI transfer/reception

-

Execute in place – XIP functionality support

-

Data Bus Size configuration to 8, 16 or 32 bits wide

-

Optional FIFO size extension

-

Maximum supported Flash address range – 32 bits

-

Up to 4 SPI slaves can be addressed

-

Software Slave Select Output – SSO – selection

-

Automatic Slave Select outputs assertion

-

System error detection

-

Interrupt generation

-

Bit rates generated as 1/ 2.. 1/255 of system clock.

-

Four SPI transfer formats supported: CPOL/CPHA.

-

Simple interface allows easy connection to microcontrollers

-

Fully synthesizable, static synchronous design with no internal tri-states

Deliverables

-

Source code:

-

VHDL Source Code or/and

-

VERILOG Source Code or/and

-

Encrypted, or plain text EDIF

-

VHDL & VERILOG test bench environment

-

Active-HDL automatic simulation macros

-

Model Sim automatic simulation macros

-

Tests with reference responses

-

Technical documentation

-

Installation notes

-

HDL core specification

-

Datasheet

-

Synthesis scripts

-

Example application

-

Technical support

-

IP Core implementation support

-

3 months maintenance

-

Delivery of the IP Core and documentation updates, minor and

-

major versions changes

-

Phone & email support

Applications

-

Embedded microprocessor boards

-

Consumer and professional audio/video

-

Home and automotive radio

-

Low-power applications

-

Communication systems

-

Digital multimeters

![]()