Description and Features

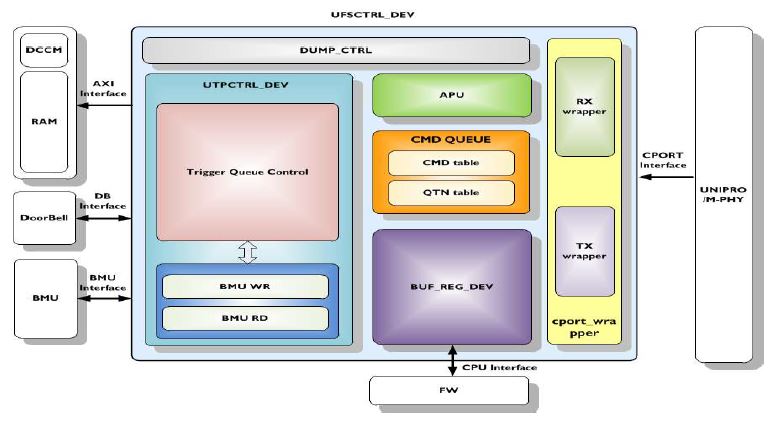

Our Universal Flash Storage (UFS) Controller IP is compliant with the latest JEDEC UFS v3.1 specification. The UFS standard is a high performance, low power serial interface that efficiently moves data between a host processor and mass storage devices.

When our UFS Controller IP is combined with in-house developed UniPro Controller IP and M-PHY IP, designers can easily integrate PHY and the controller with low risk and accelerate time-to market with our UFS IP solution.

Verification : IP Functionally is verified in NC – Verilog simulation software using testbench written in Verilog HDL

Features

-

Compliant with the JEDEC UFS v3.1

-

Backward compatibility JEDEC UFS v3.0 & v2.1

-

TAG overlap/LBA overlap/Valid UPIU check

-

Maximum DATA OUT = 64KB

-

Maximum DATA IN = 64KB

-

Maximum RTT number= 8

-

CMD Queue Depth = 32

-

HW Auto NOP IN Response

-

HW Auto Query Response

-

HW Auto Write Function

-

Support HPB v1.0 (Host-aware Performance Booster)

-

Support EHS (Extra Header Segment)

Deliverables

-

User Manual

-

Behavior model, and RTL codes

-

Test patterns and Test Documentation

Benefits

-

Write-protect options include permanent and power-on protection

-

RMM-compliant synthesizable RTL design in Verilog

-

Easy-to-use test environment

Applications

-

IOT

-

Automotive

-

Storage

-

Consumer

-

Embedded

-

Enterprise

![]()