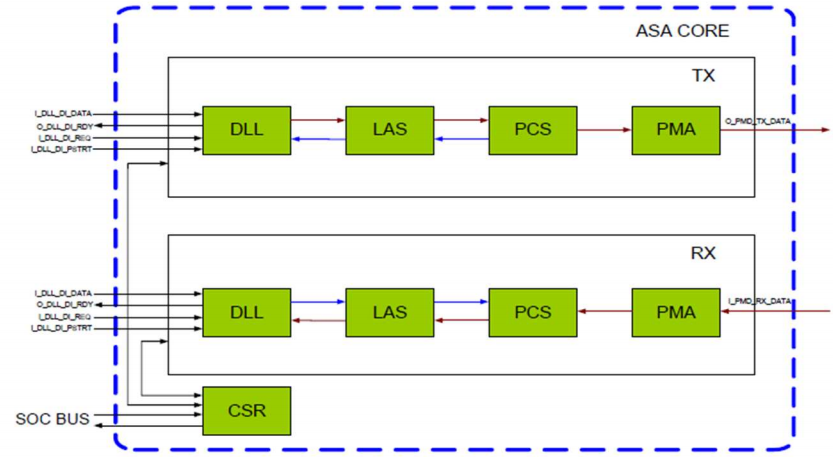

The Automotive SerDes IP Core is a fully functional, user-friendly, synthesizable design that can be effortlessly incorporated into any FPGA or SoC development. The ASA Technical Specifications 1.0, 1.1, 2.0, and 2.1 are supported by the ASA IP core. Additionally, it may handle a number of host bus interfaces, including VCI, OCP, Avalon, PLB, Tilelink, Wishbone, AMBA APB, AMBA AHB, AMBA AHB-Lite, AMBA AXI, AMBA AXI-Lite, and Custom buses, providing simple integration into any design architecture.

Supports Automotive SerDes versions 1.01, 1.1, 2.0, and 2.1.

Covers data connection, PHY layers, ASE, ASD, and OAM.

Ensures link layer security with key exchange.

Supports FOFA in normal and enumeration modes.

Half-duplex physical layer with asymmetric data rates via IBG.

Enables multiplexing/demultiplexing of internal and application data.

Compatible with eDP, I2C, Ethernet, SPI, GPIO, video, I2S, and ASEP streams.

Implements time-division access and multiple startup phases (1G, SGA, SGB, SGC).

Supports speeds from 2Gbps to 16Gbps, uplink over 100 Mbps.

Includes PCS scrambling, RS-FEC encoding, and PAM4/PAM2 mapping.

Provides MLE Ethernet with MII, GMII, and XGMII.

Uses 64b/65b and 4b/5b encoding.

Features clock recovery and light sleep mode.

Allows auto-startup in normal or test mode.

Deliverables

RTL design in Verilog

Lint, CDC, Synthesis Script with waiver files

Lint, CDC, Synthesis Reports

IP-XACT RDL generated address map

Firmware code and Linux driver package

Technical documentation in greater detail

Easy to use Verilog Test Environment with

Verilog Test cases

ISO26262 Safety Manual (SAM) Document

ISO26262 Failure Modes, Effects and

Diagnostics Analysis (FMEDA) Document