The Automotive SerDes may be verified quickly and easily with the help of the ASA Verification IP (VIP). Every year that goes by, the verification process becomes more complicated because chips are becoming more complex. Verification frequently acts as a bottleneck and might use up to 60–80% of project resources due to the growing complexity of the design. The ASA VIP offered by the T2M for Automotive SerDes, which complies completely with Automotive SerDes specifications versions 1.01, 1.1, 2.0, and 2.1 is made to ease verification of the Automotive Serdes.

Implemented in Native OpenVera, SystemVerilog, Verilog, and SystemC.

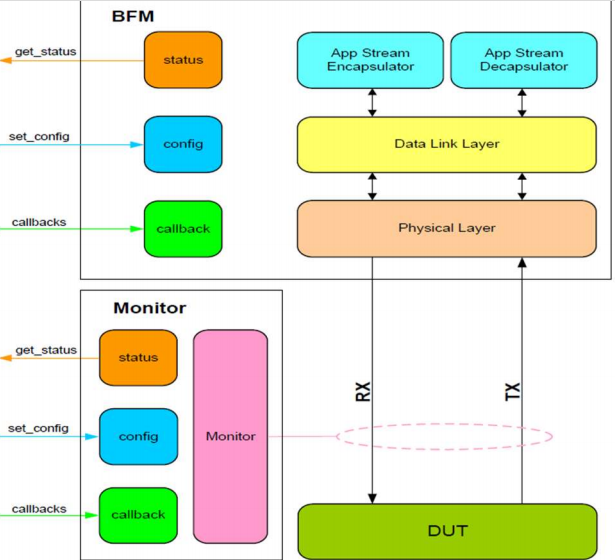

Supports RVM, AVM, VMM, OVM, UVM, and custom environments.

Compliant with Automotive SerDes spec v1.01, 1.1, 2.0, and 2.1.

Covers PHY & data link layers, ASE, ASD, OAM, security, FOFA, and IBG.

Supports multiplexing, demultiplexing, and various data streams (video, I2C, Ethernet, SPI, GPIO, eDP, I2S, CSI-2, ACC).

Implements time-division access, multiple startup phases, and speed gears (2Gbps–16Gbps).

Downlink up to 16Gbps, uplink >100Mbps, PCS scrambling, RS-FEC, PTB, PAM2/PAM4 encoding.

MLE support with MII, GMII, XGMII & 64b/65b, 4b/5b encoding.

Features clock recovery, light sleep, automatic link startup, and test mode.

Monitors events, constraints randomization, status counters, and callbacks.

Comes with a full test suite and functional coverage.

Deliverables

Complete regression suite containing all the eMMC testcases.

Examples of how to connect various components and Monitor.

Detailed documentation of all class, task and functions used in the verification environment.