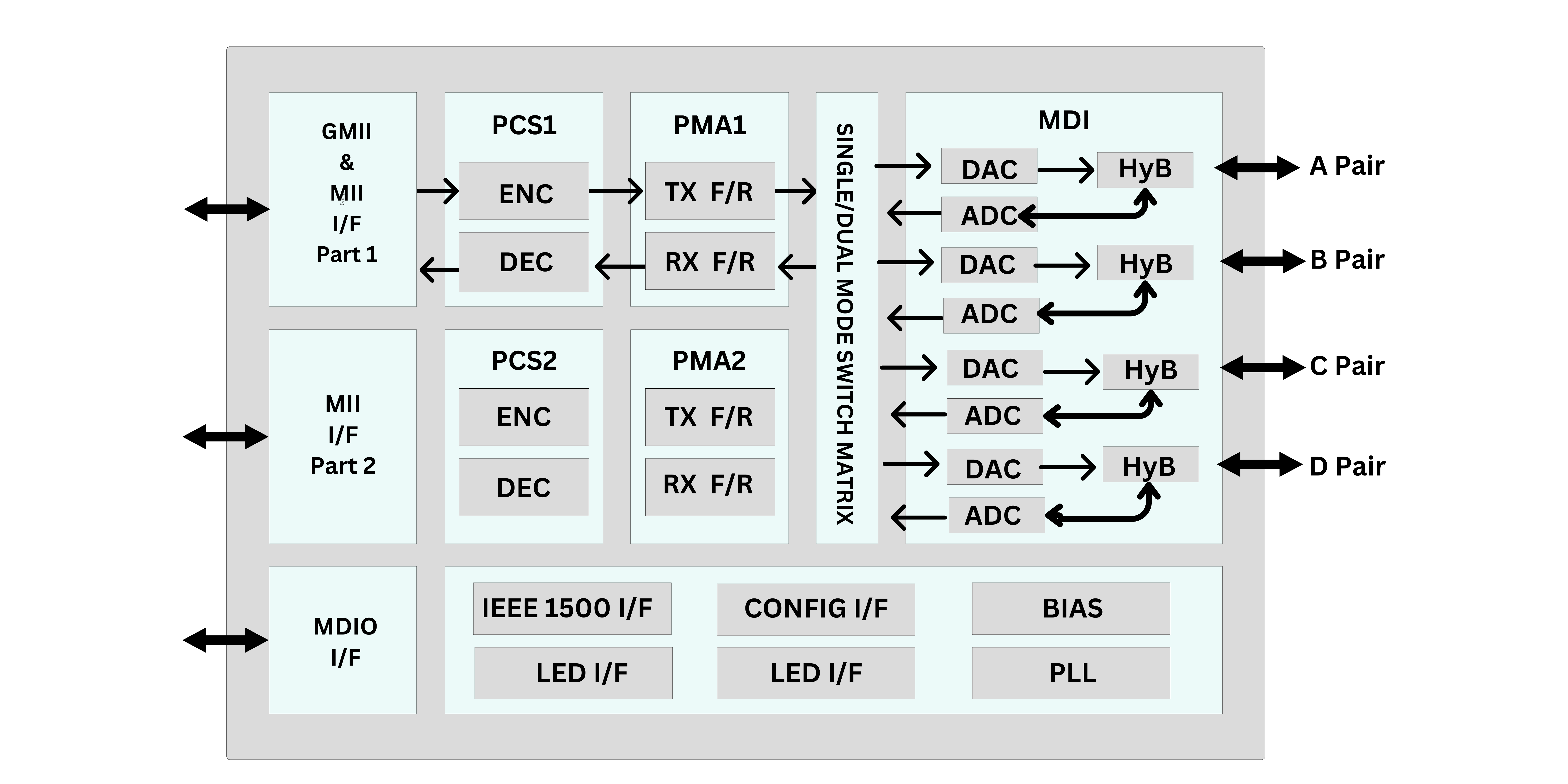

The Automotive Ethernet PHY IP Core is a 100M Ethernet PHY IP. Boasting a BroadR-Reach™ feature compatible with 100BaseT1 operations. It is a highly integrated single chip for 10/100 Ethernet application supporting 10BASE-T, 100BASE-TX, 100BASE-T1 operation. The IP connects MAC layer by GMII (Giga Media Independent Interface) or RGMII defined by IEEE 802.3ab, including the Physical Coding Sub-layer (PCS), Physical Medium Attachment Layer (PMA), Twisted Pair Physical Medium Dependent Sub-layer (TP-PMD, 100BASE-TX only).

• IEEE 802.3-2008, IEEE 802.3az fully standards compliant

• IEEE 1588-2008 support

• BroadR-Reach™ support (100BaseT1)

• Dual port MAC interface:

-GMII (10/100/1000BASE-T)

- MII (10/100BASE-T).

• Auto-negotiation support

• Automatic detection and correction of pair swaps

• (Auto-MDIX), pair skew and pair polarity

• 6 different operating modes:

- 1000BASE-T Full Duplex and Half Duplex

- 100BASE-TX/100BaseT1 Full Duplex and Half Duplex

- 10BASE-T Full Duplex and Half Duplex

• Management interface

• Baseline wander compensation

• On-chip transmit wave-shaping

• On-chip hybrid circuit

• 10KB jumbo frames

• Internal, external and remote loop back

• Hardware configuration for default operation

• Power down mode, interrupt support

• IEEE 1500 support for SoC testing integration

• LED indication: link mode, status, speed, activity, and collision

• Silicon Proven in ST 28nm FDSOI

Deliverables

• Detailed Datasheet

• Verilog behavior model (A) for simulation

• Liberty (db./.lib) for synthesis, STA, and equivalence checking

• CTL / CTLDB for DFT

• SPF (Standard Test Interface Language (STIL Procedure File) for ATPG

• LEF for APR

• CDL for LVS connection