Description

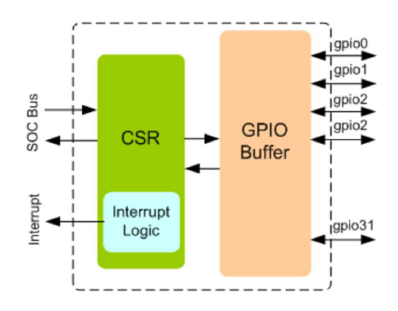

The GPIO Core is full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The GPIO Controller IP can be implemented in any technology. The GPIO Controller IP core supports the standard protocol of GPIO specifications. GPIO Controller IP also supports a variety of host bus interfaces for easy adoption into any design architecture - AHB, APB, OCP, AXI, Wishbone, VCI, Avalon, PLB, Wishbone or custom buses.

Features

-

Compliant with standard protocol of GPIO specification

-

Supports configurable for GPIO pins from 1 to 32 bits

-

Supports dynamic programming of each GPIO bit as input or output

-

Supports optional interrupt generation with configurable edge detection of the inputs (Either Rising/Falling edge)

-

Fully synthesizable.

-

Static synchronous design.

-

Positive edge clocking and no internal tri-states.

-

Scan test ready.

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

Deliverables

-

RTL design in Verilog

-

Lint, CDC, Synthesis Scripts with waiver files

-

Lint, CDC, Synthesis Reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with Verilog Testcases

![]()