Description

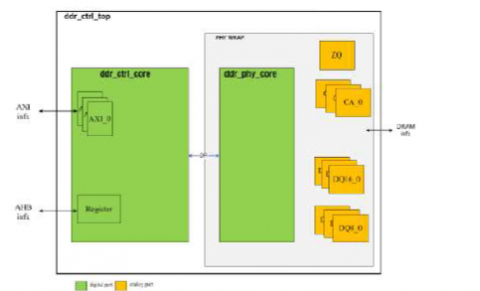

The DDR (Double Data Rate) controller IP is for LPDDR4 and DDR4/3/3L optimized for low latency. The Controller IP is silicon proven and connects to DDR PHY via the DFI 4.0 interface to provide customers a complete memory interface solution with ease of integration and faster time to market. The DDR IP is compliant with the latest JEDEC standards and is silicon proven

This memory controller supports DDR4, DDR3, DDR3L, LPDDR4 SDRAM. This memory controller is a high-speed interface used for data read/write between internal engine and outside SDRAM bus, and transfers the internal signal to meet the SDRAM specification. In order to have more large memory space for ASIC IC to store, it is better for low cost to store memory to external DRAM. So DDR (Double Data Rate) controller is needed. All engines in ASIC IC can store any information and data through DDR controller to DRAM by using AXI interface.

For Write : DDR controller transfers write command/address and data of engines from AXI interface to DRAM interface and write data into DRAM. For Read : DDR controller transfers read command/address of engines from AXI interface to DRAM interface. After DRAM gets Read command/address, DRAM will transform data to DDR controller by DRAM interface, and then DDR controller helps to transfer the data to data owner engine by AXI interface.

Features

-

Support DDR3 / DDR3L / DDR4/ 3DS DDR4/ LPDDR4 / MRAM

-

Support x8/x16/x32 DRAM data bus configuration (programmable)

-

Support Multi-Ranks DRAM configuration

-

DDR base on DFI spec 4.0 compliant.

-

Clock speed : 800MHz(DFI_CLK) / 500MHz(AXI_CLK)

-

Support SRAM parity or ECC protection (option)

-

AHB register interface support

-

Support core power island switched off in low power mode

-

Weighted round-robin AXI arbiter support

-

Support embedded Build-In-Self-Test (BIST)

-

Support 6 AXI channel (programmable)

-

Support AXI data bus width 128bit/256bit

-

Support ECC/CRC data path protection (option)

-

Support write or read data retry when errors are triggered

-

Support PHY training (ZQ training, VREF training,

-

write-leveling training, gate training, W/R data

-

window training)

-

Support dynamic PHY delay line code compensation

-

for PVT variation

-

Support PHY Internal Loop Back for CP/FT

-

Support CA mirror and DQ swapping to reduce PCB layout effort

-

Support DDR4 CT mode for on board manufacture testing

Benefits

-

DDR Controller IP functionality is verified in NC-Verilog simulation software using test bench written in

-

Verilog HDL

-

High performance

-

Low power

-

Low gate count

-

Highly flexible, scalable, configurable

-

Ease of integration

Applications

-

SSD Controller

-

TV

-

Setup Box

-

Multimedia

-

Mobile

-

Data centers (networking and storage)

-

Servers

-

High-performance computing

-

Surveillance

-

IOT

Deliverables

-

User Manual

-

Behavior model, and protected RTL codes

-

Synopsys library (LIB)

-

Test patterns and Test Documentation

![]()