Description

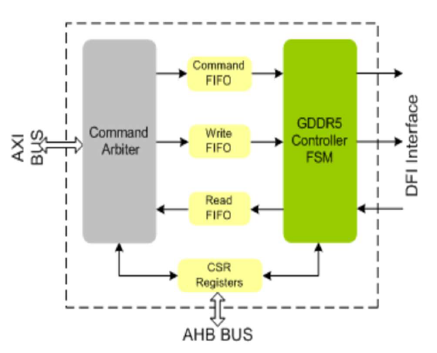

GDDR5 interface provides full support for the GDDR5 interface, compatible with standard JESD212C specification and DFI-version 4.0 or 5.0 Specification Compliant. Through its GDDR5 compatibility, it provides a simple interface to a wide range of lowcost devices. GDDR5 IP is proven in FPGA environment. The host interface of the GDDR5 can be simple interface or can be AMBA AHB, AMBA AHBLite, AMBA APB, AMBA AXI, AMBA AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or Custom protocol.

Features

-

Supports GDDR5 protocol standard JESD212C.

-

Compliant with DFI-version 4.0 or 5.0 Specification.

-

Supports all the GDDR5 commands as per the specs.

-

Supports up to 16 AXI ports with data width upto 512 bits.

-

Supports controllable outstanding transactions for AXI write and read channels

-

Supports in port arbitration and multi-port arbitration.

-

Supports user programmable page policy. • Closed page policy • Open page policy

-

Supports Error Checking and correction (ECC).

-

Supports retry on ECC error, with retry limit user controllable.

-

Supports high clock speeds in ASIC and FPGA.

-

Supports low latency for write and read path.

-

Supports reordering of transactions for higher performance.

-

Supports for programmable clock frequency of operation.

-

Supports for all types of timing and protocol violation detection.

-

Supports 512MB, 1GB, 2GB, 4GB, 8GB Package Pin out and addressing,

-

Supports X16, X32 device modes

-

Supports for All Mode registers programming.

-

Supports for Single ended interface for command, address and data.

-

Supports Double Data Rate (DDR) data (WCK).

-

Supports Single Data Rate (SDR) command (CK).

-

Supports Double Data Rate (DDR) addressing (CK).

-

Supports for QDR and DDR operating mode.

-

Supports for Programmable Burst length:8,16.

-

Supports for Programmable read latency and write latency.

-

Supports for Write data mask function via address bus.

-

Supports for Data bus inversion (DBI) & address bus inversion (ABI).

-

Supports for Input/output PLL/DLL.

-

Supports for Address training.

-

Supports for cyclic redundancy check (CRC-8).

-

Supports for Programmable CRC read latency, write latency.

-

Supports for Low Power modes.

-

Supports for Auto & self-refresh modes.

-

Supports for On-die termination (ODT) for all highspeed inputs.

Deliverables

-

The GDDR5 interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()