Description and Features

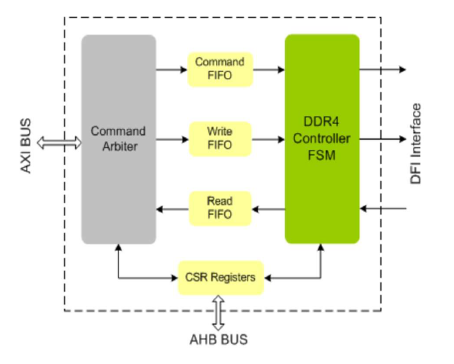

DDR4 is full-featured, easy-to-use, synthesizable design, compatible with DDR4 JESD79-4, JESD79-4A, JESD79-4A_r2, JESD79-4B, JESD79-4C and JESD79-4D (Draft) specification and DFI-version 3.0 or higher Specification Compliant. Through its DDR4 compatibility,it provides a simple interface to a wide range of low-cost devices. DDR4 IP is proven in FPGA environment.The host interface of the DDR4 can be simple interface or can be AMBA AHB, AMBA AHBLite, AMBA APB, AMBA AXI, AMBA AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or Custom protocol.

Features

-

Supports DDR4 protocol standard JESD79-4, JESD79- 4A, JESD79-4A_r2, JESD79-4B, JESD79-4C and JESD79-4D (Draft) Specification.

-

Compliant with DFI-version 3.0 or higher Specification.

-

Supports up to 16 AXI ports with data width upto 512 bits.

-

Supports controllable outstanding transactions for AXI write and read channels

-

Supports in port arbitration and multi-port arbitration.

-

Supports user programmable page policy. • Closed page policy, Open page policy

-

Supports Error Checking and correction (ECC).

-

Supports retry on ECC error, with retry limit user controllable.

-

Supports high clock speeds in ASIC and FPGA.

-

Supports low latency for write and read path.

-

Supports reordering of transactions for higher performance.

-

Supports up to 16GB device density.

-

Supports X4, X8, X16 and X32 devices.

-

Supports all speed grades as per specification.

-

Supports Mode Registers programming.

-

Supports On-the-fly protocol and data checking.

-

Supports Programmable Preamble.

-

Supports Read preamble training.

-

Supports burst order.

-

Supports Programmable Write latency and Read latency.

-

Supports Programmable burst length of 4 and 8.

-

Supports the following burst types: • Sequential, Interleave

-

Supports Multiple Outstanding transaction.

-

Supports In-port Arbitration using QoS.

-

Supports write transaction with Data Mask and (DBI) Data Bus Inversion.

-

Supports read transaction with (DBI) Data Bus Inversion.

-

Supports Fine Granularity Refresh Mode.

-

Supports CRC and ECC for Write and Read Operations.

-

Supports Command Address Parity features.

-

Supports both Synchronous and Asynchronous On- Die Termination modes.

-

Supports Power Down features and Maximum Power Saving mode.

-

Supports 1:4 Controller to DFI PHY frequency ratio.

Deliverables

-

The DDR4 interface is available in Source and netlist products.

-

The Source product is delivered in Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()