Description

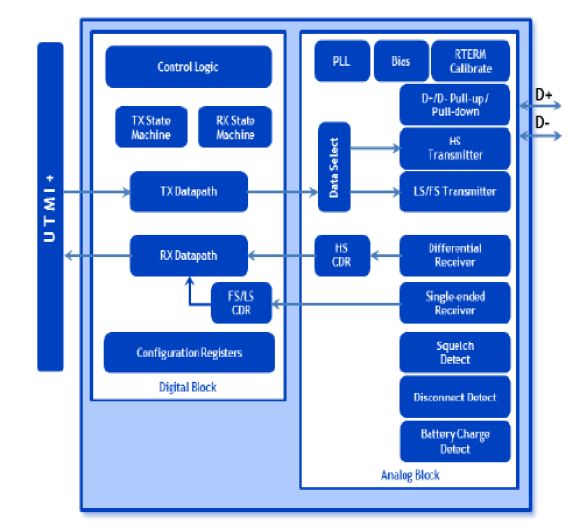

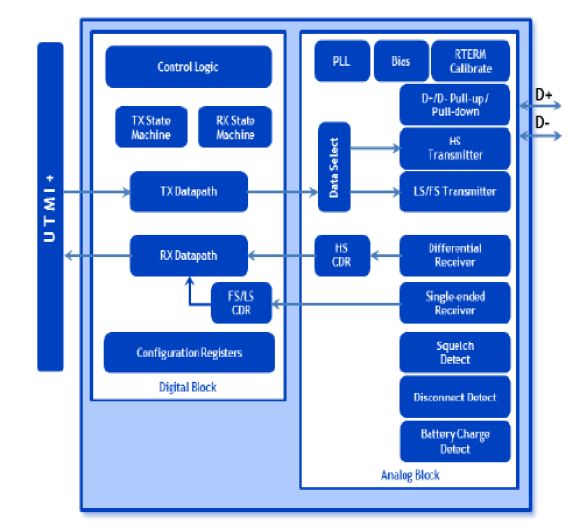

The USB 2.0 PHY IP is a complete physical layer (PHY) IP solution designed for low power and peak performance. The USB2.0 IP implements a High-Speed USB 2.0 transceiver for use with either host, device and OTG function controllers. Compliant with the UTMI+ level 3 specification, the USB2.0 PHY IP integrates mixed-signal circuits to support High-Speed data rate at 480Mbps and is backward compatible to Full-Speed (12Mbps) and Low-Speed (1.5Mbps) data rates. Targeting mobile and consumer product applications, the USB2.0 PHY IP also supports the supplementary USB Battery Charging specifications. The USB 2.0 PHY IP is available in different Fabs / Nodes such as “TSMC 28HPC+, TSMC 40LP, TSMC 40LL, UMC 28HPC, UMC 40LP, UMC 55SP, UMC 55EF, SMIC 14SF+, SMIC 40LL, SMIC 55LL”.

The USB 2.0 PHY IP transceiver is optimized for low power consumption and minimal die area without sacrificing performance and high-data throughput. The USB2.0 PHY IP comprises a complete on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, clock generation block provided by an internal PLL, and a resistor termination calibration circuit to ensure full support for host and device functionality.

Features

-

Compliant with USB2.0 and USB1.1 specification

-

Compliant with UTMI Specification Version level 3.

-

Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

-

All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

16-bit, 30MHz or 8-bit, 60MHz parallel interface for HS/FS

-

Serializing for transmitting data stream and Deserializing for receiving data stream

-

USB Data Recovery and Clock Recovery on receiving

-

Integrated Bit Stuffing and NRZI encoding for Transmit

-

Integrated Bit Un-Stuffing and NRZI decoding for Receive

-

SYNC and EOP generation on transmit packets and detection on receive packets

-

Internal reference resistor that replaces the external reference resistor

-

Built in self test for production testing

-

Supports USB suspend state and remote wakeup

-

Supports detection of USB reset, suspend and resume signaling

-

Supports high speed identification and detection as defined by USB 2.0 Specification

-

Support high speed host disconnection detection

-

Silicon Proven in TSMC 28nm, TSMC 40nm, UMC 28nm, UMC 40nm, UMC 55nm, SMIC 14nm, SMIC 40nm, SMIC 55nm

Deliverables

-

Application Note / User Manual

-

Behavior model, and protected RTL codes

-

Protected Post layout netlist and Standard

-

Delay Format (SDF)

-

Frame view (LEF)

-

Metal GDS (GDSII)

-

Test patterns and Test Documentation

Benefits

-

Smallest area size

-

Fully compliant with Universal Serial Bus (USB) 2.0 electrical specifications

-

Compliant with UTMI+ specification (High-Speed, Full-Speed and Low-Speed functions)

-

Supports clock inputs from 10/12/25/30MHz crystal oscillator or external 10/12/25/30MHz clock source

-

Integrated PLL to provide a variety of stand-alone clock outputs for USB related applications

Applications

-

PC

-

Television

-

Data storage

-

Multimedia Devices

-

Recorders

-

Mobile devices