Description

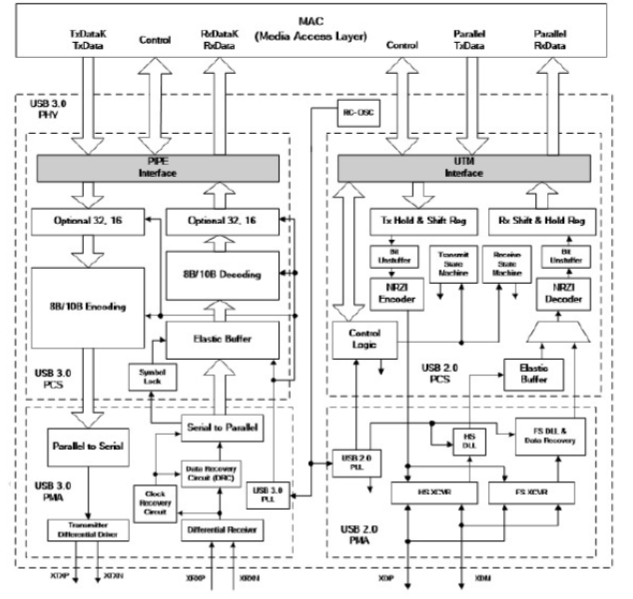

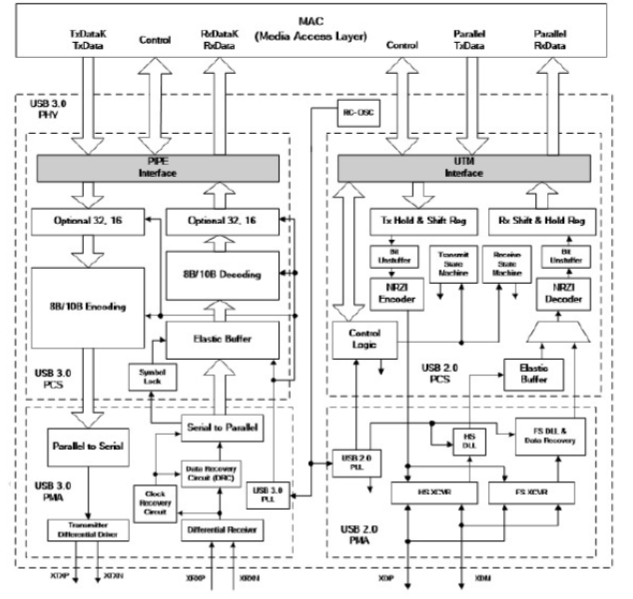

This is a Universal Serial Bus (USB) transceiver which is provided for peripheral devices. The PHY is compliant with the USB 3.0 (USB SuperSpeed),USB 2.0 PIPE and UTMI specifications. The USB3.0 PHY IP transceiver is optimized for low power consumption and minimal die area without sacrificing performance and highdata throughput. The USB3.0 PHY IP comprises a complete on-chip physical transceiver solution with Electro Static Discharge (ESD) protection, built-in self test module with embedded jitter injection, and a dynamic equalization circuit that ensures full support for high-performance designs. Standard PHY interface (PIPE) enables multiple IP sources for USB3 MAC layer. Allowable analog circuit parameter adjustment and internal test control Built-in Self Test with embedded Jitter Injection Output Jitter reduction with constant power technique.

The USB 3.0 PHY IP is available in different Fabs / Nodes such as “TSMC 28HPC+, UMC 28HPC, UMC 28HPC+, UMC 40LP, SMIC 14SF+”.

Features

-

Compliant with Universal Serial Bus 3.0 Specification

-

Supports 2.5GT/s and 5.0GT/s serial data transmission rate

-

Compliant with PIPE 3.0

-

Compliant with Universal Serial Bus 2.0 Specification

-

High-speed data transfer rate: 480 Mbps

-

Compliant with legacy USB 1.1

-

Full-speed data transfer rate: 12 Mbps

-

Compliant with UTMI 1.05 Specification

-

UMC 40nm LP 1P7M1T1H (LVT/RVT/HVT) process

-

Operating Voltage: 1.1V and 3.3V

-

Support low jitter automatically calibrated oscillator for crystal-less mode

-

Support 125/250 MHz with 32/16-bit mode for USB 3.0

-

Support the Build-In-Self-Test (BIST) mode for low cost TEG/ATE testing

-

Silicon Proven in TSMC 28nm, UMC 28nm, UMC 40nm, SMIC 14nm

Deliverables

-

GDSII & layer map

-

Place-Route views (.LEF)

-

Liberty library (.lib)

-

Verilog behavior model

-

Netlist & SDF timing

-

Layout guidelines, application notes

-

LVS/DRC verification reports

Benefits

-

Power Consumption: <70mW in Super Speed

-

Physical Area: < 0.30mm2

-

Operating Temperature: ~40degrees~125degrees

-

IP Module Area: 0.285mm2

Applications

-

PC, Television

-

Data storage

-

Multimedia Devices

-

Recorders

-

Mobile device