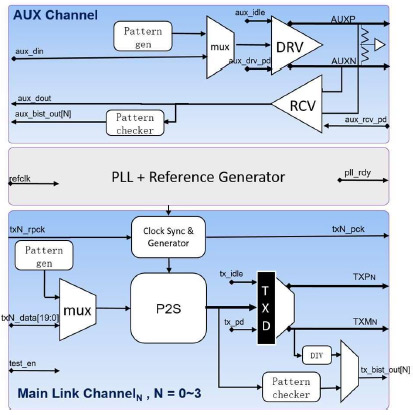

eDP/DP Tx PHY is designed for chips that perform eDP/DP data communication while operating at low power consumption. The main link is a multi-gigabit transmitter macro which enable speed up to 4.0Gbps data transmitter with optimized power and die size, also it can be easily fabricated and implemented in a video system. The AUX channel is a half-duplex, bidirectional channel consisting of one differential pair, supporting the bit rate of about 1Mbps.

Macro consists of multi-main link transmitter channels, AUX channel, one PLL and bias-gen unit. The main link transmitter performs dedicated P2S, clock generator, driver with pre-emphasis and self-test. Each of the channels can be turned off individually.

Deliverables