Description

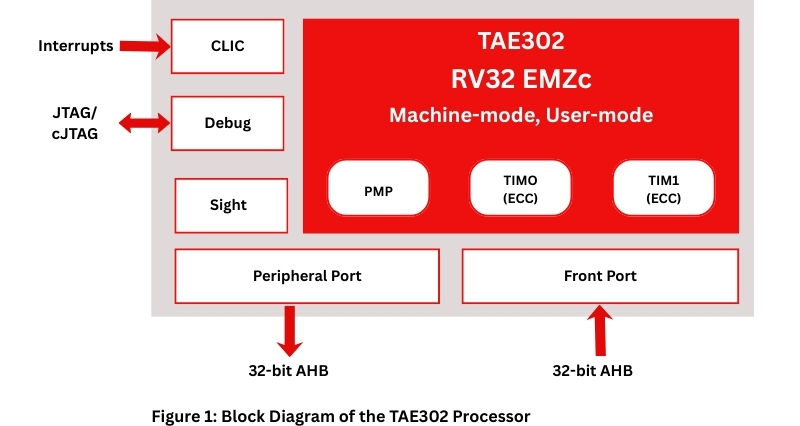

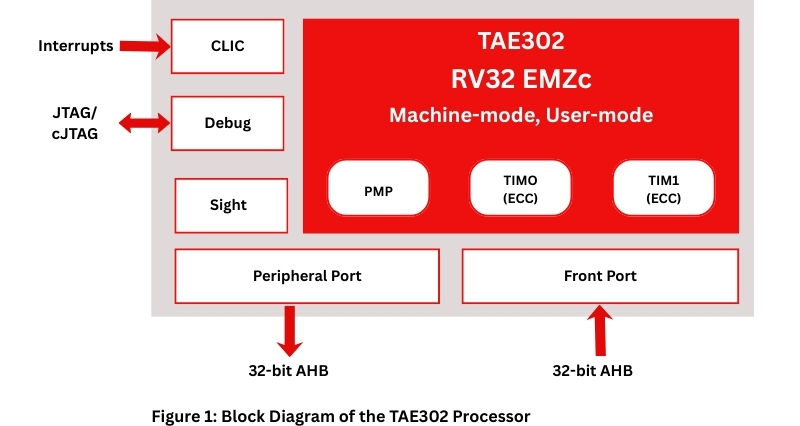

A 32-bit RISC-V embedded functional safety processor. Parity/ECC and Stack Pointer Monitor (SPM) modules are added based on the TGE302, compliant with ASIL-B functional safety standards.

Sight: Provides waveform debugging tools, so that users can easily understand the internal state and events of the CPU.

Features

-

ISA: RISC-V 32-bit EMZc

-

Modes: Machine-mode, User-mode

-

Security: PMP Region can optional from 0 to 16 Pipeline 3-stage pipeline

-

TIM: TIM0 and TIM1,with configurable sizes from 0KB to 128MB, ECC optional

-

Interrupt : CLIC interrupt controller, supports 112 interrupt requests and non-maskable interrupts (NMI)

-

Debug: Debug module, supports JTAG/cJTAG

-

Bus Interface

-

Peripheral Port: 32-bit AHB master interface

-

Front port: 32-bit AHB slave interface, used for external access to TIM0 and TIM1

-

CoreMark (CoreMarks/MHz): 3.25

-

Dhrystone-Legla (DMIPS/MHz): 1.47

Application

-

Display

-

Industry

-

Consumer Electronics

-

Vehicle

-

Power management, etc

Deliverables

-

Synthesizable RISC-V CPU IP core

-

Simulation Environment with test case demo

-

IP User Manual/ Integration Manual/ Simulation Manual/ Functional Safety Manual (if support)

-

FPGA Development Board Support Package

-

FPGA board

-

User manual

-

Online technical support

-

Offline technical support

-

IDE Package

-

IDE (Windows + Linux versions)

-

User guides

-

Pre-built tool suite

-

Pre-built project demos

-

Automated debug and trace process

-

Toolchain Package

-

GCC13/GCC14-based toolchain

-

Compiler, assembler, linker

-

QEMU simulator

-

GDB debugger

-

Basic libraries

-

SDK

-

MCU SDK (EMSIS, RTOS support, RTOS interrupt nesting support, etc.) for 32-bit IPs

-

Linux SDK (Linux OS support) for 64-bit IPs