Description

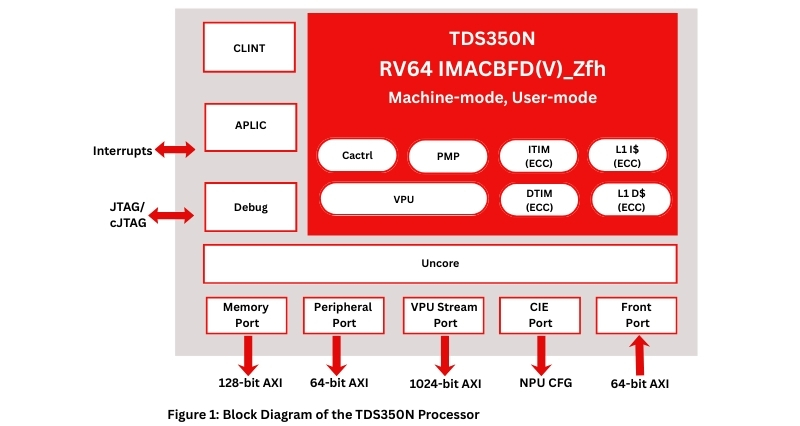

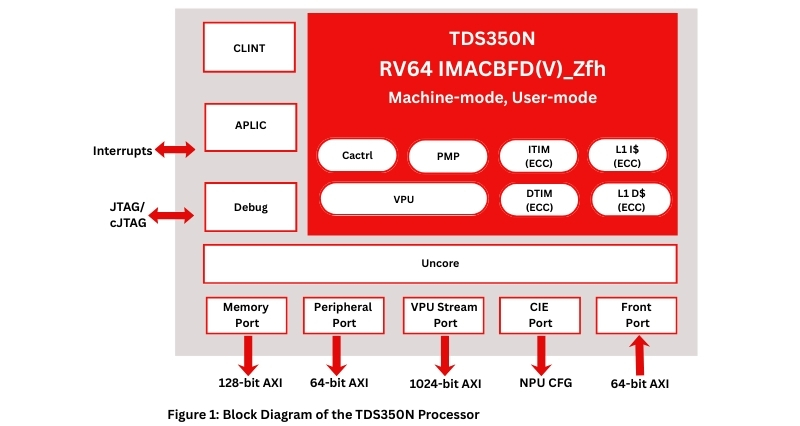

TDS350N is a 64-bit RISC-V AI acceleration processor designed for artificial intelligence and machine learning scenarios, which achieves energy efficiency optimization while ensuring high-performance computing. The processor is developed based on the RISC-V standard vector extension (RVV1.0) architecture, supports 1024-bit vector length computing capabilities, and can efficiently complete the data pre-processing/post-processing tasks required by the neural network processor (NPU) or graphics processor (GPU), significantly reducing the workload of heterogeneous computing units and improving the overall efficiency of the system.

Features

-

ISA: RISC-V 64-bit IMACBFD(V)_Zfh

-

Modes: Machine-mode, U-mode

-

Security: Supports Smepmp,PMP Regioncan beconfigured from 0 to 64

-

Pipeline: 8-stage superscalar in-order pipeline, 2-way decode

-

Vector: Supports RVV1.0, maximum width 1024-bit

-

CIE Port: Supports CIE coprocessor instruction extension interface

-

TIM: ITIM and DTIM, with configurable sizes from 0KB to 128KB, ECC optional

-

L1 I$: Configurable size (8K/16K/32K), ECC optional

-

L1 D$: Configurable size (8K/16K/32K), ECC optional

-

Interrupt: Supports CLINT and APLIC (AIA+PLIC)

-

Debug: Debug module supportsJTAG/cJTAG

-

Bus Interface:

-

Memory Port: 128 -bit AXI master interface

-

Peripheral Port: 64-bit AXI master interface

-

VPU Stream Port: 1024 -bit AXI master interface

-

CIE Port: NPU CFG

-

Front Port: 64-bit AXI slave interface

-

CoreMark (CoreMarks/MHz): 5.2

-

Dhrystone-Legal (DMIPS/MHz): 2.5

Application

-

Smart Security

-

Embodied intelligence

-

Autonomous driving

-

Smart industrial control markets, etc

Deliveables

-

IP Package

-

Synthesizable RISC-V CPU IP core

-

Simulation Environment with test case demo

-

IP User Manual/ Integration Manual/ Simulation Manual/ Functional Safety Manual (if support)

-

FPGA Development Board Support Package

-

FPGA board

-

User manual

-

Online technical support

-

Offline technical support

-

IDE Package

-

IDE (Windows + Linux versions)

-

User guides

-

Pre-built tool suite

-

Pre-built project demos

-

Automated debug and trace process

-

Toolchain Package

-

GCC13/GCC14-based toolchain

-

Compiler, assembler, linker

-

QEMU simulator

-

GDB debugger

-

Basic libraries

-

SDK

-

MCU SDK (EMSIS, RTOS support, RTOS interrupt nesting support, etc.) for 32-bit IPs

-

Linux SDK (Linux OS support) for 64-bit IPs