Description

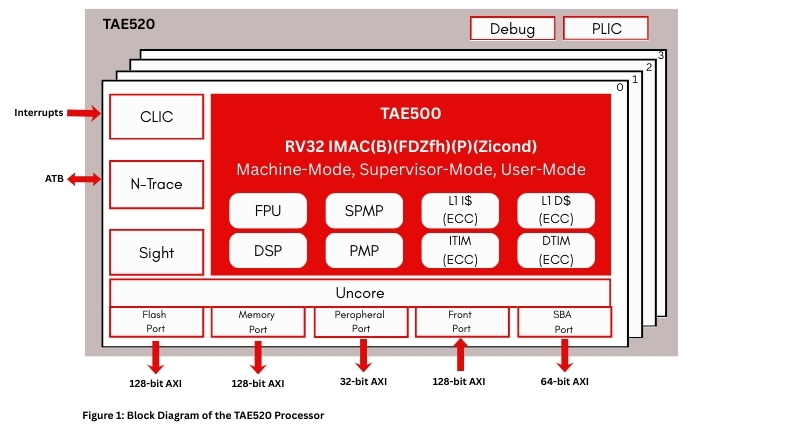

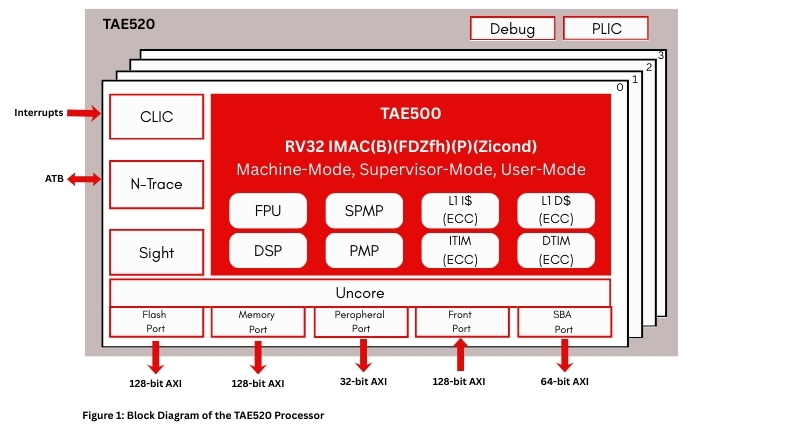

A high-performance 32-bit RISC-V embedded-level CPU IP. Based on TAE500 single core, build DCLS functional security architecture, support Split/Lock mode. Compliant with the ISO-26262 automotive safety standard and supports ASIL-D automotive safety certification.

Sight: Provides waveform debugging tools to give users easy insight into key signals within the CPU.

Features

-

ISA: RV32 IMAC(B)(FDZfh)(P)_Zicsr_Zifencei_Zicbom_(Zicond)_Zilsd

-

Modes: Machine-Mode, Supervisor-Mode (optional), User-Mode

-

Pipeline: 6-stage in-order superscalar pipeline with BP (Branch Predictor)

-

FPU: Optional FPU (Floating-Point Unit) supports half-precision, single-precision and double-precision floating-point

-

DSP: Optional DSP (Digital Signal Processing) unit supports SIMD (Single Instruction Multiple Data) instruction, supports full RV32P Expansion

-

Security:

-

Supports Smepmp. Optional PMP (Physical Memory Protection) with configurable regions from 0 to 16

-

Optional SPMP (S-mode Physical Memory Protection) with configurable regions from 0 to 16

-

Supports PPMA (Programmable Physical Memory Attributes) checking

-

L1 I$: L1 I$ (L1 Instruction Cache) size is configurable from 4KB to 128KB, 2-way set associative, 64B Cacheline, ECC optional

-

L1 D$: L1 D$ (L1 Data Cache) size is configurable from 4KB to 128KB, 4-way set associative, 64B Cacheline, ECC optional

-

ITIM: Optional ITIM (Instruction Tightly-Integrated Memory) with configurable size from 0KB to 16MB. ECC optional

-

DTIM: Optional DTIM (Data Tightly-Integrated Memory) with configurable size from 0KB to 16MB. ECC optional

-

Interrupt:

-

Supports CLIC interrupt controller with up to 1008 fast interrupts per core

-

Supports PLIC interrupt controller with up to 1024 external interrupt sources

-

Supports recoverable non-maskable interrupt (NMI)

-

Debug:

-

Debug module supports JTAG/cJTAG port, supports SBA (System Bus Access) function

-

Trigger module supports up to 16 hardware breakpoints

-

Supports Sight function for insight into core signal assisted debug

-

Trace: Optional trace module supports RISC-V N-Trace

-

Bus Interface: One 128-bit read-only AXI master interface for Flash XIP, one 128-bit AXI master interface, one 32-bit AXI master interface, one 128-bit AXI slave interface and one 64-bit AXI master interface

-

CoreMark (CoreMarks/MHz): 5.81

-

Dhrystone-Legal (DMIPS/MHz): 2.83

Applications

-

Automotive

-

Robotics

-

High-speed storage systems

-

Industrial control, etc.

Deliverables

-

Synthesizable RISC-V CPU IP core

-

Simulation Environment with test case demo

-

IP User Manual/ Integration Manual/ Simulation Manual/ Functional Safety Manual (if support)

-

FPGA Development Board Support Package

-

FPGA board

-

User manual

-

Online technical support

-

Offline technical support

-

IDE Package

-

IDE (Windows + Linux versions)

-

User guides

-

Pre-built tool suite

-

Pre-built project demos

-

Automated debug and trace process

-

Toolchain Package

-

GCC13/GCC14-based toolchain

-

Compiler, assembler, linker

-

QEMU simulator

-

GDB debugger

-

Basic libraries

-

SDK

-

MCU SDK (EMSIS, RTOS support, RTOS interrupt nesting support, etc.) for 32-bit IPs

-

Linux SDK (Linux OS support) for 64-bit IPs