Description

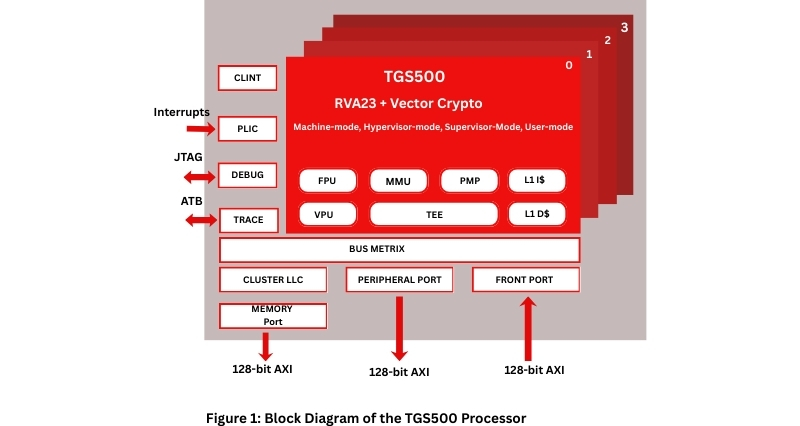

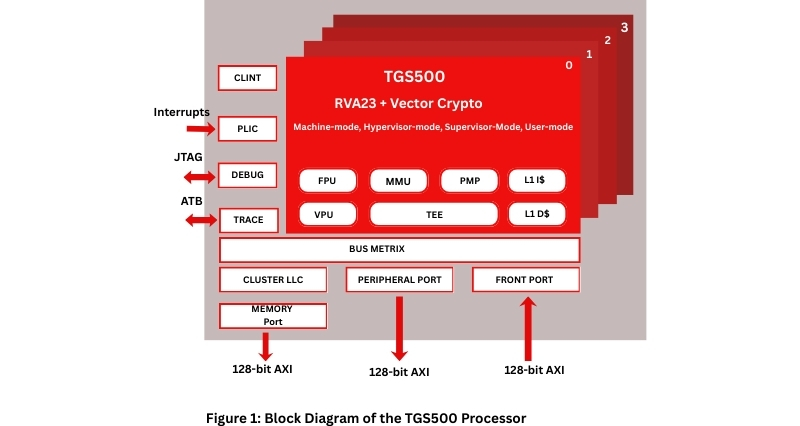

A high energy efficiency 64-bit RISC-V application-grade general-purpose processor that compliant with RVA23-Profile.

Features

-

ISA: RVA23+Vector Crypto

-

Multi-core: Single core, dual core, 4 core options

-

Modes: Machine-mode, Hypervisor-mode, Supervisor-mode, User mode

-

Security: Supports TEE solution, with up to 64 PMP regions

-

Crypto: Supports optional scalar, vector hardware encryption and decryption module

-

Pipeline: 9-stage superscalar in-order pipeline, 2-way decod

-

Branch Predictor: L0_BTB, BTB, IJTB, BHT, RAS, Loop Buffer

-

L1 I$: Size is configurable from 8KB to 64KB

-

L1 D$: Size is configurable from 8KB to 64KB

-

Cluster LLC: Size is configurable from 256KB to 4MB

-

MMU: SV39, ITLB, DTLB

-

Interrupt: CLINT, PLIC

-

Debug:

-

Debug module: supports JTAG

-

Trace module: supports RISC-V standard E-Trace/ N-Trace

-

Bus Interface:

-

Memory Port: 128–bit AXI master interface

-

Peripheral Port: 128-bit AXI master interface

-

Front port: 128-bit AXI slave interface

-

CoreMark (CoreMarks/MHz): 6.27

-

Dhrystone-Legla (DMIPS/MHz): 2.90

Applications

-

Mobile terminals

-

Display devices

-

AIoT edge computing

-

Network devices and baseband communications.

Deliverables

-

Synthesizable RISC-V CPU IP core

-

Simulation Environment with test case demo

-

IP User Manual/ Integration Manual/ Simulation Manual/ Functional Safety Manual (if support)

-

FPGA Development Board Support Package

-

FPGA board

-

User manual

-

Online technical support

-

Offline technical support

-

IDE Package

-

IDE (Windows + Linux versions)

-

User guides

-

Pre-built tool suite

-

Pre-built project demos

-

Automated debug and trace process

-

Toolchain Package

-

GCC13/GCC14-based toolchain

-

Compiler, assembler, linker

-

QEMU simulator

-

GDB debugger

-

Basic libraries

-

SDK

-

MCU SDK (EMSIS, RTOS support, RTOS interrupt nesting support, etc.) for 32-bit IPs

-

Linux SDK (Linux OS support) for 64-bit IPs