Description

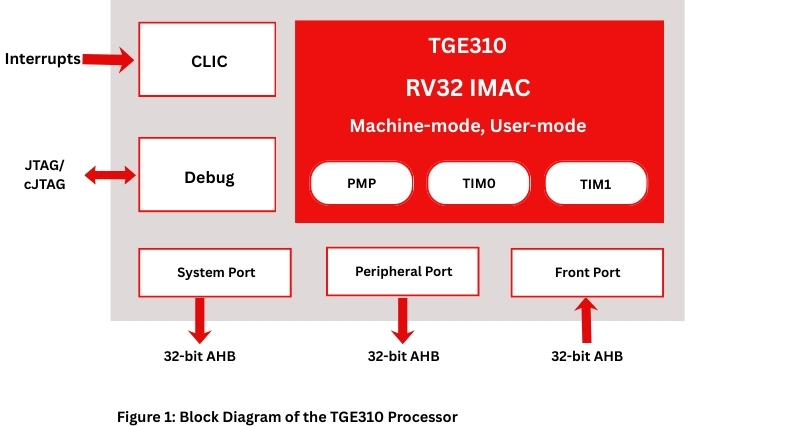

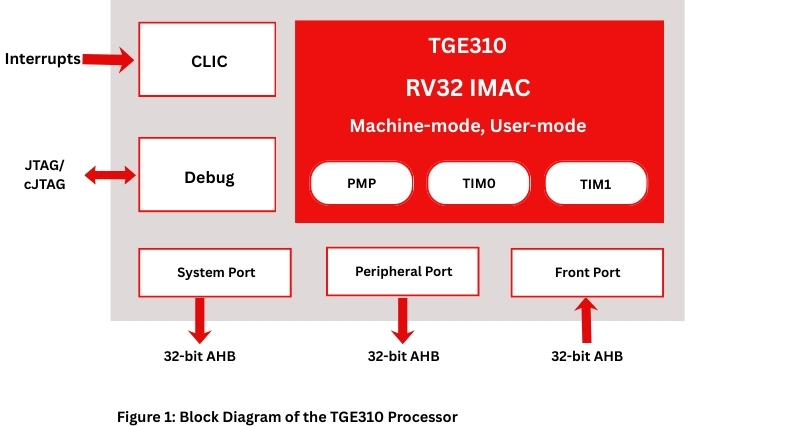

A low power, high cost-effective 32-bit RISC-V embedded general purpose processor.

Features

-

Architecture: RISC-V RV32IMAC_Zicsr_Zifencei instruction set

-

Pipeline: 3-stage pipeline (Fetch, Execute, Writeback)

-

Operating Modes: Machine Mode, User Mode

-

Hardware Multiplier & Divider: Supported

-

Security: Optional Physical Memory Protection (PMP) with up to 16 configurable memory regions

-

Memory: Optional Tightly-Integrated Memory (TIM0, TIM1), each configurable from 0KB to 128MB

-

Interrupt System:

-

Core Local Interrupt Controller (CLIC) with up to 112 fast interrupts

-

Non-Maskable Interrupt (NMI) and CLIC software interrupt support

-

Debug Support:

-

JTAG/cJTAG interface

-

Up to 16 hardware breakpoints

-

Compatible with GDB, OpenOCD, TRACE32, Segger J-Link, IAR, FTDI

-

Bus Interfaces:

-

Two 32-bit AHB master and one 32-bit AHB slave interfaces

-

Supports RISC-V Atomic (A) extension and clock division up to 1/10

-

Hardware Performance Monitor (HPM):

-

64-bit counters for cycles, instructions, and up to 29 configurable events

-

Power Management:

-

Supports WFI (Wait for Interrupt) instruction and low-power mode indication

-

CoreMark (CoreMarks/MHz): 3.58

-

Dhrystone-Legla (DMIPS/MHz): 1.59

Applications

-

Display Screen

-

Automotive

-

Consumer electronics Markets

Deliverables

-

Synthesizable RISC-V CPU IP core

-

Simulation Environment with test case demo

-

IP User Manual/ Integration Manual/ Simulation Manual/ Functional Safety Manual (if support)

-

FPGA Development Board Support Package

-

FPGA board

-

User manual

-

Online technical support

-

Offline technical support

-

IDE Package

-

IDE (Windows + Linux versions)

-

User guides

-

Pre-built tool suite

-

Pre-built project demos

-

Automated debug and trace process

-

Toolchain Package

-

GCC13/GCC14-based toolchain

-

Compiler, assembler, linker

-

QEMU simulator

-

GDB debugger

-

Basic libraries

-

SDK

-

MCU SDK (EMSIS, RTOS support, RTOS interrupt nesting support, etc.) for 32-bit IPs

-

Linux SDK (Linux OS support) for 64-bit IPs